# INTRODUCTION TO VLSI DESIGN WITH SYSTEM ON CHIP DESIGN REUSE: $\mbox{A TUTORIAL FOR STUDENTS}$

by

Frank J. Ventura Jr.

An Applied Project in Partial Fulfillment of the Requirements for the Degree Master of Science in Technology

ARIZONA STATE UNIVERSITY EAST

March 2005

# INTRODUCTION TO VLSI DESIGN WITH SYSTEM ON CHIP DESIGN REUSE: A THIORIAL FOR STUDENTS

|                       | A TOTORIAL FOR STUDENTS  |        |

|-----------------------|--------------------------|--------|

|                       |                          |        |

|                       | by                       |        |

|                       | Frank J. Ventura Jr.     |        |

|                       | has been approved        |        |

|                       | March, 2005              |        |

|                       |                          |        |

|                       |                          |        |

| APPROVED:             |                          |        |

|                       |                          | ,Chair |

| Dr. Narciso F. Macia  |                          |        |

| Dr. Albert L. McHenry |                          |        |

| Dr. Don Cottrell      |                          |        |

|                       | Supervisory Committee    |        |

|                       |                          |        |

|                       | ACCEPTED:                |        |

|                       |                          |        |

|                       | Dr. Lakshmi V. Munukutla |        |

Department Chair

## **ABSTRACT**

Due to the absence of a formal class in VLSI design at ASU East, the need arose for a hands-on tutorial that would introduce the students to VLSI design, emphasizing System-on-a-Chip design and the concept of design reuse.

When UET 513 – Introduction to VLSI Design was taught at ASU East, The Western Design Center Inc. (WDC) supported this class by donating industry used software tools and their microprocessor Intellectual Property (IP) for the class to use in learning the concepts of VLSI Design. WDC continues to support the students at ASU East that are interested in VLSI design, by offering internships to give the students experience in the VLSI design flow. Students interested in using this tutorial will be able to work at WDC's office and have access to the software tools and technology. The students will be following the design flow as used by WDC. The students will be exposed to the following design tools: ViewDraw for schematic entry, Silos for Verilog HDL simulation, ICED for laying out an IC, and PSPICE for electrical characterization. These tools, used in conjunction with the microprocessor technology of WDC, provide the students with a hands-on experience in VLSI design methodology. The students will also learn the value of design reuse by utilizing the standard cell library created by WDC.

The tutorial that was created introduces the students to the tools, concepts, methodology, and history of VLSI design. The students will gain hands-on experience by performing exercises related to each step of the VLSI design flow as it is used in industry. Thus, the students' introduction to VLSI design with system-on-a-chip design reuse will be complete.

# **DEDICATION**

This project is dedicated to my parents, Frank and Lorraine Ventura, and my family for all of their support.

## **ACKNOWLEDGEMENTS**

I would like to thank my committee, Dr. Narciso F. Macia, Dr. Albert L. McHenry and Dr. Don Cottrell for your patience, support and input on this project.

Special thanks to William D. Mensch Jr. of The Western Design Center, Inc. for allowing me to use the 65xx technology and WDC's design tools, and for all the support, guidance and technical assistance that you have provided to me.

I would also like to thank the following people, who in some way were involved in getting me through this project: Lou Prado, Lars Dannemann, Dianne Mensch, Jack Daniels, Dr. Rajeswari Sundararajan, Linda Deutsch, Four Peaks, Prakash Moparthi, Sam Buca, Anna Wales and Betsy Allen.

# TABLE OF CONTENTS

| LIST OF F  | FIGURES                                                 | VIII |

|------------|---------------------------------------------------------|------|

| LIST OF T  | TABLES                                                  | X    |

| 1. INTROI  | DUCTION                                                 | 1    |

|            | ACKGROUND                                               |      |

|            | ROBLEM                                                  |      |

|            |                                                         |      |

|            | COPE                                                    |      |

|            | SSUMPTIONS                                              |      |

| 2. VLSI DI | ESIGN FLOW                                              | 6    |

| 2.1 D      | DESIGN ENTRY                                            | 6    |

| 2.1.1      | Schematic entry                                         |      |

| 2.1.2      |                                                         |      |

| 2.1.2      | 2.1 VHDL                                                |      |

| 2.1.2      |                                                         |      |

| 2.1.3      | Introduction to ViewDraw                                |      |

| 2.1.3      | - · · · · · · · · · · · · · · · · · · ·                 |      |

|            | ESIGN SIMULATION                                        |      |

|            | Introduction to Silos                                   |      |

|            | 1.1 Introduction to simulating a design using Silos     |      |

|            | HYSICAL LAYOUT OF THE DESIGN                            |      |

|            | Introduction to ICED                                    |      |

|            | CALING AND SIZING THE DESIGN (RETARGETING)              |      |

|            | LECTRICAL CHARACTERIZATION AND TIMING ANALYSIS          |      |

|            | Description of PSPICE simulation setup                  |      |

|            | 1.1 The PSPICE simulation files                         |      |

|            | 1.2 Setting up the PSPICE simulation                    |      |

|            | Further comments on retargeting and simulating a design |      |

| 2.6 Fabr   | LICATING THE DESIGN                                     | 56   |

|            | The MOSIS Integrated Circuit fabrication service        |      |

| 2.7 Testi  | ING THE PACKAGED PARTS                                  | 58   |

| 2.7.1 I    | n-house testing                                         | 58   |

| 2.7.2 7    | Testing on automated testers                            | 59   |

| 3. SYSTEM  | M ON A CHIP DESIGN TUTORIAL                             | 60   |

|            | ODUCTION TO THE W65C122S SYSTEM CHIP                    |      |

| 3.2 W650   | C122S PIN DESCRIPTIONS                                  |      |

| 3.2.1      | Address Bus (A0-A15)                                    |      |

| 3.2.2      | Bus Enable (BE)                                         |      |

| 3.2.3      | Control Lines (CA1, CA2)                                |      |

| 3.2.4      | Control Lines (CB1, CB2)                                |      |

| 3.2.5      | Data Bus (D0-D7)                                        |      |

| 3.2.6      | External Memory (EXTMEMB)                               |      |

| 3.2.7      | FCLK                                                    |      |

| 3.2.8      | Interrupt Request (IRQB)                                |      |

| 3.2.9      | No Connect (NC)                                         |      |

| 3.2.10     | 1 ' '                                                   |      |

| 3.2.11     | Peripheral Data Port A (PA0-PA7)                        | 64   |

| 3.2.12 Periph      | neral Data Port B (PB0-PB7)                             | 64  |

|--------------------|---------------------------------------------------------|-----|

| 3.2.13 PHI2.       |                                                         | 64  |

| 3.2.14 Power       | · Supply (VDD, VSS)                                     | 64  |

| 3.2.15 Read/\      | Write (RWB)                                             | 65  |

| 3.2.16 Ready       | (RDY)                                                   | 65  |

| 3.2.17 Reset (     | (RESB)                                                  | 65  |

| 3.2.18 Synchi      | ronize (SYNC)                                           | 65  |

| 3.3 WORKING WITH   | I THE W65C122S SCHEMATIC USING VIEWDRAW                 | 66  |

| 3.3.1 Introduction | on to the W65C122S Schematic                            | 66  |

| 3.3.2 Extracting   | a Verilog Netlist of the W65C122S                       | 72  |

|                    | IE W65C122S USING SILOS                                 |     |

| 3.4.1 Working w    | ith the W65C122S Silos simulation directory             | 76  |

| 3.4.2 Setting up   | the simulation using the extracted schematic netlist    | 78  |

| 3.4.3 Comparing    | g the simulation results to the 'gold standard' results | 82  |

| 3.5 WORKING WITH   | THE W65C122S USING ICED LAYOUT EDITOR                   | 83  |

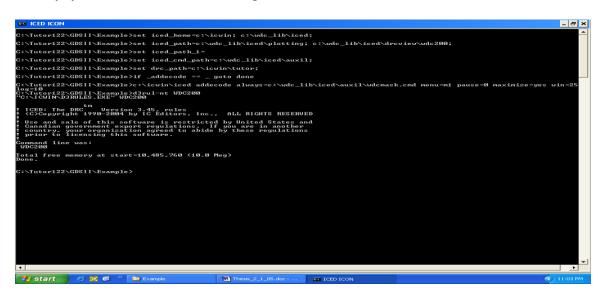

| 3.5.1 Viewing th   | e W65C122S layout in ICED                               | 84  |

| 3.5.2 Performing   | g a DRC on the W65C122S Core Layout                     | 90  |

| 3.5.3 Running N    | LE on the design                                        | 95  |

| 3.5.4 Running L    | VS on the design                                        | 98  |

| 3.6 RETARGETING    | THE W65C122S TO A DIFFERENT FOUNDRY PROCESS             | 100 |

| 3.6.1 Sizing the   | WDC 2μ design rules to target design rules              | 101 |

| 3.6.2 Scaling the  | W65C122S using ICED                                     | 101 |

| 3.6.3 Post retarg  | geting steps                                            | 105 |

| 3.7 Using PSPICE   | TO VERIFY DEVICE FUNCTIONALITY                          | 106 |

| 3.7.1 Converting   | g the extracted spice netlist to PSPICE format          | 106 |

|                    | the PSPICE simulation                                   |     |

| 3.8 SENDING THE F  | INAL DESIGN TO BE MANUFACTURED                          | 109 |

| 3.8.1 Sending the  | e design to the foundry for full production run         | 110 |

| 3.9 REAL WORLD A   | PPLICATION EXAMPLE                                      | 112 |

| 3.9.1 Licensing a  | and using 65xx IP                                       | 112 |

| 4. CONCLUSIONS     | AND RECOMMENDATIONS                                     | 114 |

| 4.1 CONCLUSIONS    |                                                         | 11/ |

|                    | TIONS                                                   |     |

|                    |                                                         |     |

| REFERENCES         |                                                         | 116 |

| APPENDIX           |                                                         | 117 |

| A1. CONTACT INFO   | RMATION FOR THE WESTERN DESIGN CENTER, INC.             | 117 |

|                    | REGARDING INTERNSHIPS AT THE WESTERN DESIGN CENTER, INC |     |

# LIST OF FIGURES

| FIGURE 1.1 W DC FLOW CHART FOR SOC DESIGN, MANUFACTURING AND TEST       |    |

|-------------------------------------------------------------------------|----|

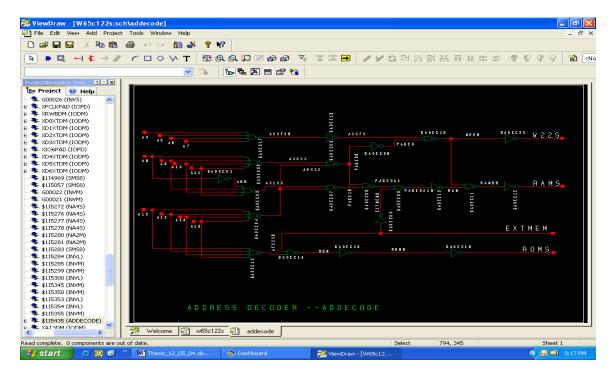

| FIGURE 2.1 EXAMPLE OF SCHEMATIC ENTRY – W65C122S ADDRESS DECODER        | 7  |

| FIGURE 2.2 COMPARISON OF VHDL AND VERILOG FOR A SERIAL ADDER/SUBTRACTOR | 10 |

| FIGURE 2.3 EPD DASHBOARD MAIN WINDOW                                    | 11 |

| FIGURE 2.4 EPD NEW PROJECT WINDOW                                       | 12 |

| FIGURE 2.5 EPD DASHBOARD VIEW OF PROJECTS                               | 13 |

| FIGURE 2.6 EPD ADD LIBRARY WINDOW                                       | 14 |

| FIGURE 2.7 EPD LIBRARY WINDOW                                           | 14 |

| FIGURE 2.8 EPD DASHBOARD VIEW WITH BUILTIN LIBRARY ADDED                | 15 |

| FIGURE 2.9 EPD DASHBOARD VIEW OF COMPLETE VDEXAMPLE PROJECT             | 15 |

| FIGURE 2.10 VIEWDRAW MAIN WELCOME WINDOW                                | 16 |

| FIGURE 2.11 VIEWDRAW NEW SCHEMATIC WINDOW                               | 17 |

| FIGURE 2.12 VIEWDRAW SCHEMATIC WINDOW                                   | 17 |

| FIGURE 2.13 VIEWDRAW ADD COMPONENT WINDOW                               |    |

| FIGURE 2.14 VIEWDRAW ADD COMPONENT WITH PREVIEW WINDOW                  | 19 |

| FIGURE 2.15 SYMBOL PLACEMENT ON SCHEMATIC                               | 19 |

| FIGURE 2.16 VIEWDRAW SCHEMATIC WINDOW WITH ADDED COMPONENTS             | 20 |

| FIGURE 2.17 SCHEMATIC ZOOM VIEW                                         | 21 |

| FIGURE 2.18 EXAMPLE OF SCHEMATIC WITH COMPONENTS CONNECTED              | 22 |

| FIGURE 2.19 EXAMPLE OF COMPLETED SCHEMATIC                              |    |

| FIGURE 2.20 NET PROPERTIES WINDOW                                       | 24 |

| FIGURE 2.21 SCHEMATIC WITH NET NAMES VISIBLE                            | 24 |

| FIGURE 2.22 SCHEMATIC WITH ALL NET NAMES VISIBLE                        | 25 |

| FIGURE 2.23 SILOS MAIN WINDOW                                           |    |

| FIGURE 2.24 NEW PROJECT WINDOW IN SILOS                                 |    |

| FIGURE 2.25 SILOS PROJECT PROPERTIES WINDOW                             | 30 |

| FIGURE 2.26 SILOS TEXT EDITOR WINDOW                                    | 31 |

| FIGURE 2.27 4-BIT ADDER VERILOG MODEL (ADDER.V)                         | 31 |

| FIGURE 2.28 TEST BENCH FOR THE 4-BIT FULL ADDER (TEST_BENCH.V)          | 32 |

| FIGURE 2.29 SILOS PROJECT PROPERTIES WINDOW                             | 33 |

| FIGURE 2.30 SILOS PROJECT PROPERTIES WINDOW WITH ADDED FILES            | 34 |

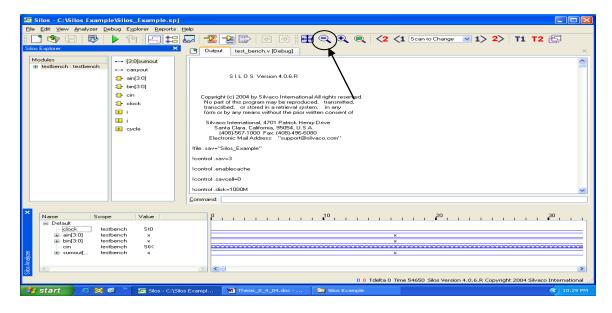

| FIGURE 2.31 SILOS SIMULATION RESULT WINDOW                              | 34 |

| FIGURE 2.32 SILOS ANALYZER AND EXPLORER WINDOW VIEW                     | 35 |

| FIGURE 2.33 ADDING SIGNALS TO THE ANALYZER                              | 36 |

| FIGURE 2.34 ANALYZER WINDOW WITH CLOCK SIGNAL ADDED                     | 36 |

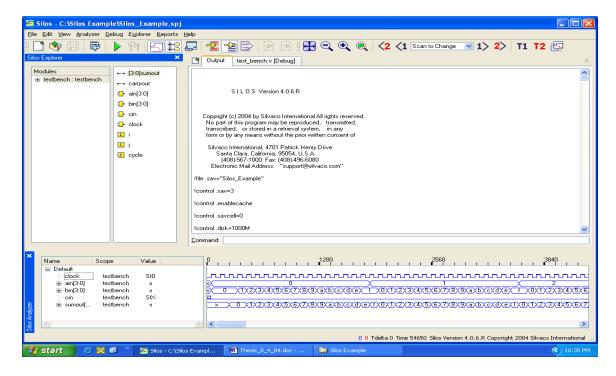

| FIGURE 2.35 ANALYZER WINDOW ALL SIGNALS ADDED                           | 37 |

| FIGURE 2.36 ANALYZER WINDOW WITH SIGNALS VIEWABLE                       | 38 |

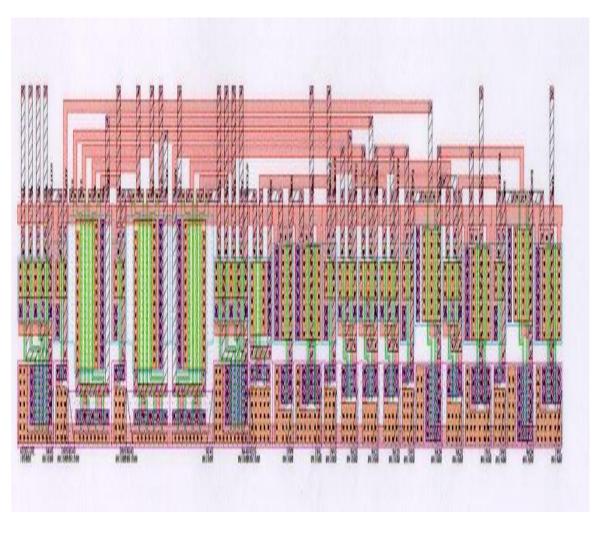

| FIGURE 2.37 PHYSICAL LAYOUT OF THE W65C122S ADDRESS DECODER             | 39 |

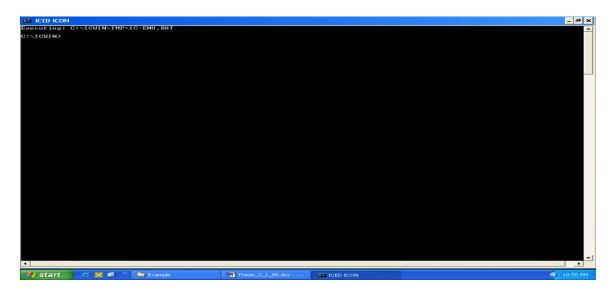

| FIGURE 2.38 ICED ICON DOS WINDOW                                        | 43 |

| FIGURE 2.39 ICED EDITOR WINDOW                                          | 43 |

| FIGURE 2.40 ICED EDITOR WINDOW SHOWING LAYER MENU                       | 44 |

| FIGURE 2.41 ICED EDITOR WINDOW SHOWING N-WELL                           |    |

| FIGURE 2.42 ICED EDITOR WINDOW SHOWING N-WELL AND POLY LAYERS           |    |

| FIGURE 2.43 ICED EDITOR WINDOW SHOWING NMOS TRANSISTOR                  | 46 |

| FIGURE 2.44 ICED EDITOR WINDOW WITH TEXT ON DRAWING                     | 46 |

| FIGURE 2.45 PSPICE MAIN WINDOW                                          |    |

| FIGURE 2.46 PSPICE WAVEFORM WINDOW                                      |    |

| FIGURE 2.47 PSPICE ADD TRACE WINDOW                                     |    |

| FIGURE 2.48 PSPICE WAVEFORM WINDOW WITH SIGNALS DISPLAYED               |    |

| FIGURE 3.1 BLOCK DIAGRAM OF THE W65C122S                                |    |

| FIGURE 3.2 W65C122S VIEWDRAW PROJECT WINDOW                             |    |

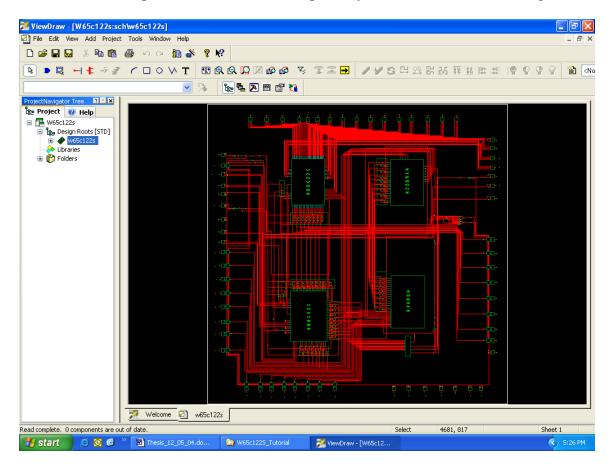

| FIGURE 3.3 W65C122S SCHEMATIC IN VIEWDRAW                               | 67 |

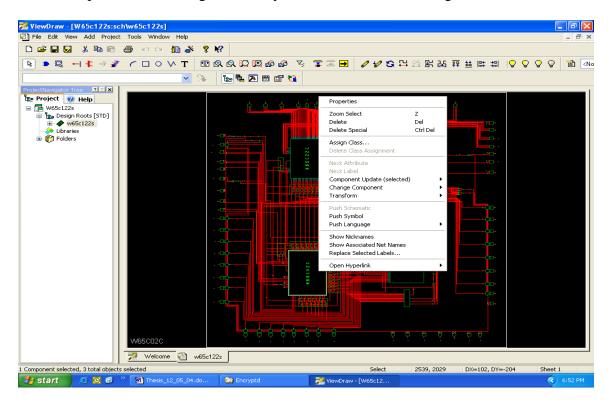

| FIGURE 3.4 SYMBOL POP-OUT MENU                                              | 68  |

|-----------------------------------------------------------------------------|-----|

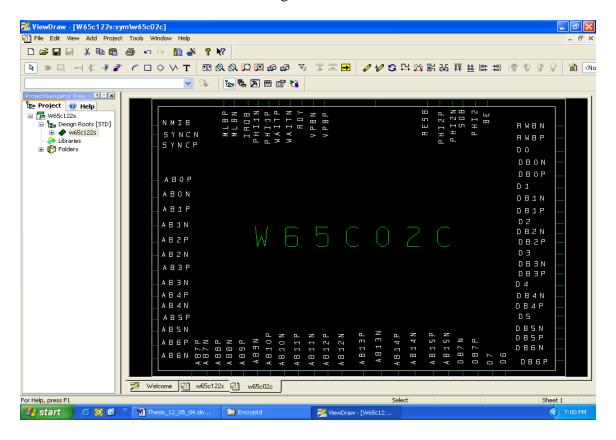

| FIGURE 3.5 W65C02C VIEWDRAW SYMBOL                                          | 69  |

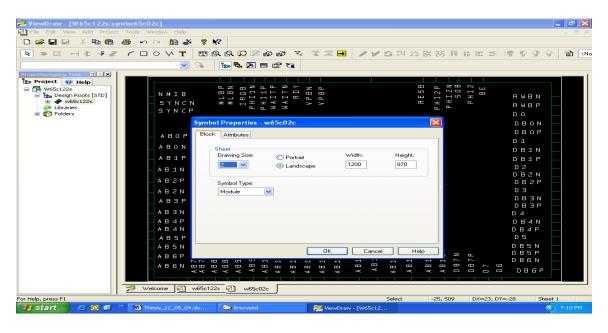

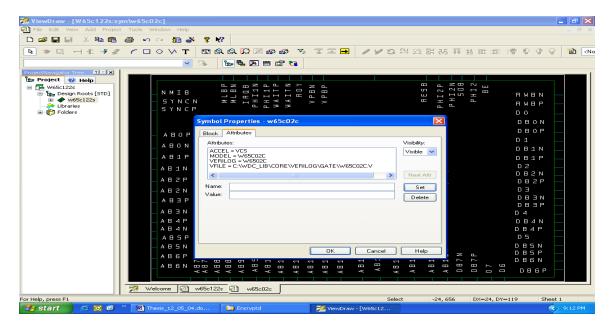

| FIGURE 3.6 SYMBOL PROPERTIES WINDOW                                         | 70  |

| FIGURE 3.7 SYMBOL ATTRIBUTE WINDOW                                          | 70  |

| FIGURE 3.8 SCHEMATIC OF THE ADDRESS DECODER                                 | 72  |

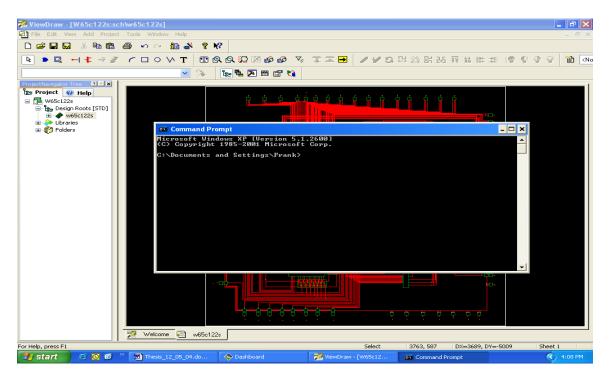

| FIGURE 3.9 DOS WINDOW FOR USING VERILNET                                    | 73  |

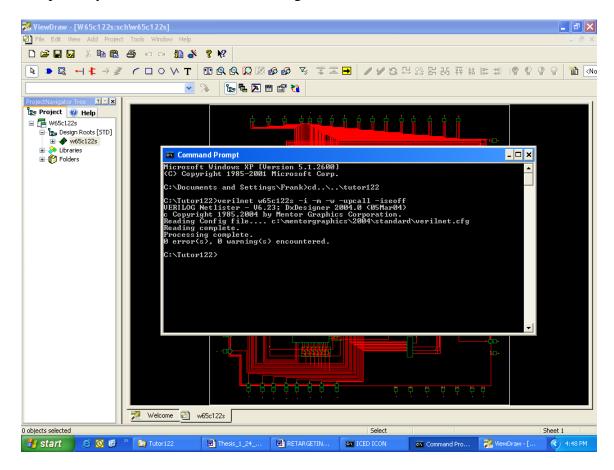

| FIGURE 3.10 VERILNET RESULTS WINDOW                                         |     |

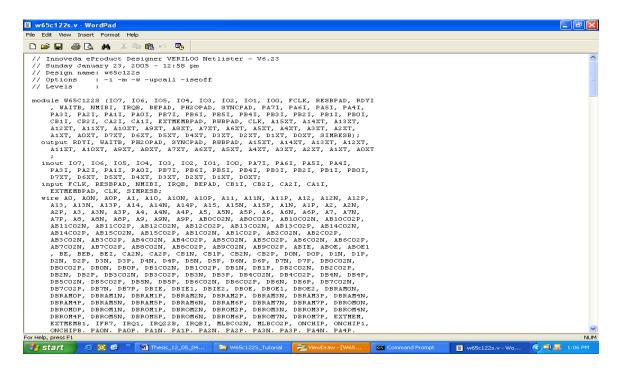

| FIGURE 3.11 EXTRACTED VERILOG NETLIST OF THE W65C122S SCHEMATIC             | 75  |

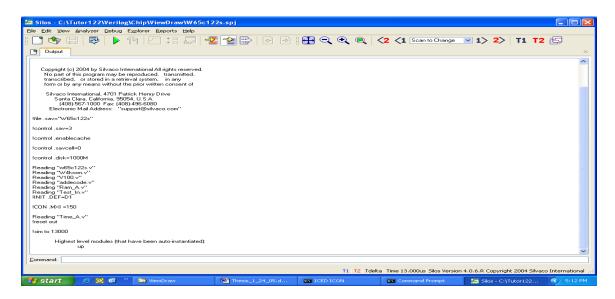

| FIGURE 3.12 SILOS MAIN WINDOW                                               |     |

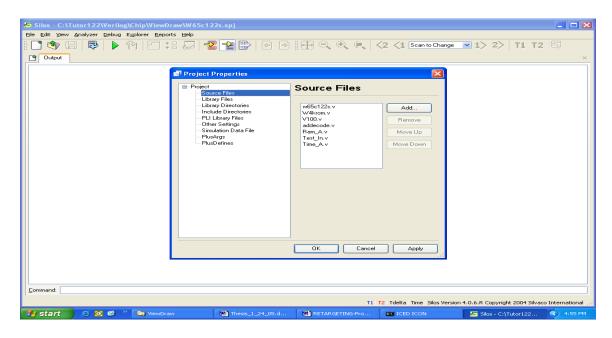

| FIGURE 3.13 SILOS PROJECT PROPERTIES DIALOG BOX FOR THE W65C122S SIMULATION | 77  |

| FIGURE 3.14 SILOS PROJECT WINDOW                                            |     |

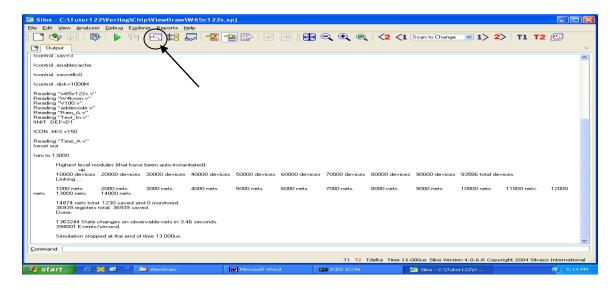

| FIGURE 3.15 SCREENSHOT OF SIMULATION IN PROGRESS                            |     |

| FIGURE 3.16 SCREENSHOT OF COMPLETED SIMULATION                              | 80  |

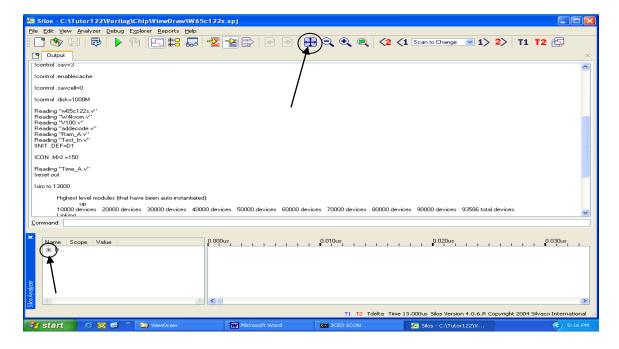

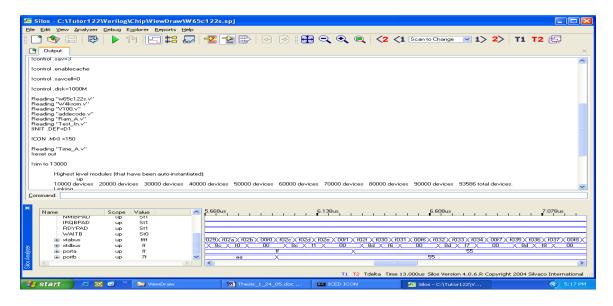

| FIGURE 3.17 SILOS WITH DATA ANALYZER WINDOW                                 | 80  |

| FIGURE 3.18 SIMULATION WAVEFORM VIEW                                        |     |

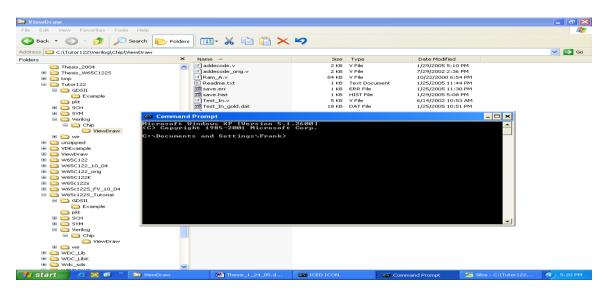

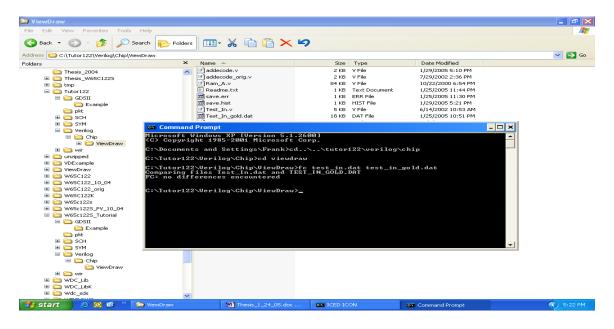

| FIGURE 3.19 DOS WINDOW                                                      | 82  |

| FIGURE 3.20 RESULTS OF FILE COMPARISON                                      | 83  |

| FIGURE 3.21 ICED DOS WINDOW                                                 |     |

| FIGURE 3.22 ICED WINDOW WITH WORKING DIRECTORY                              | 85  |

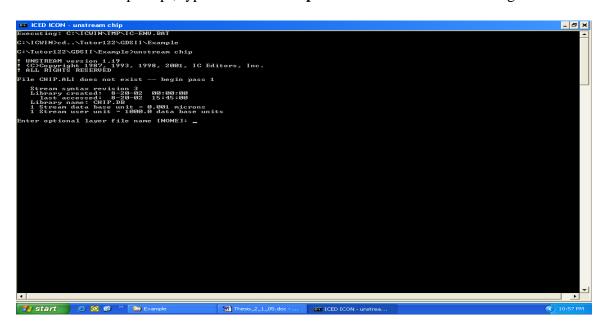

| FIGURE 3.23 ICED UNSTREAM WINDOW                                            |     |

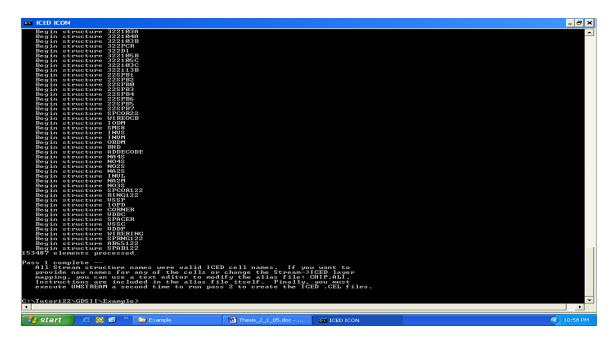

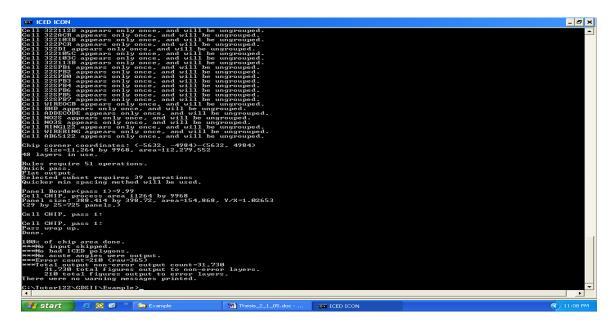

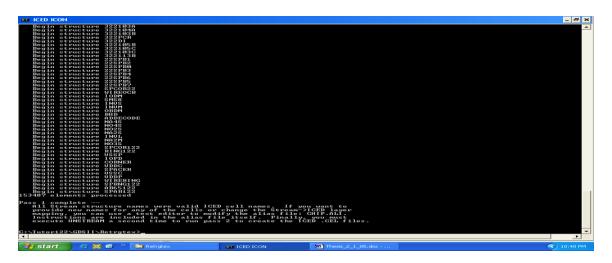

| FIGURE 3.24 DOS WINDOW AT THE COMPLETION OF PASS 1                          | 86  |

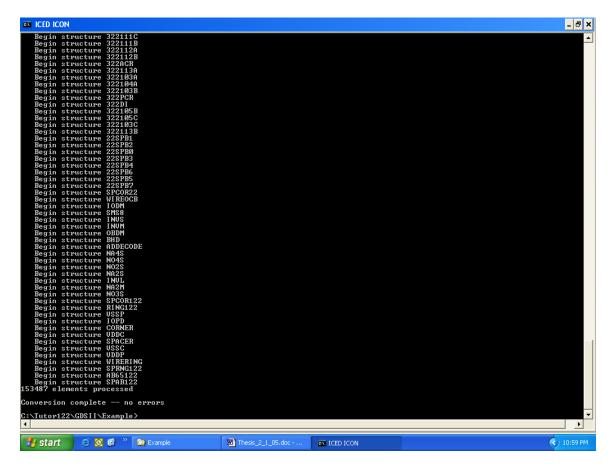

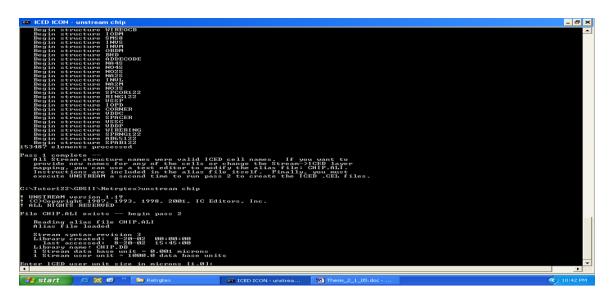

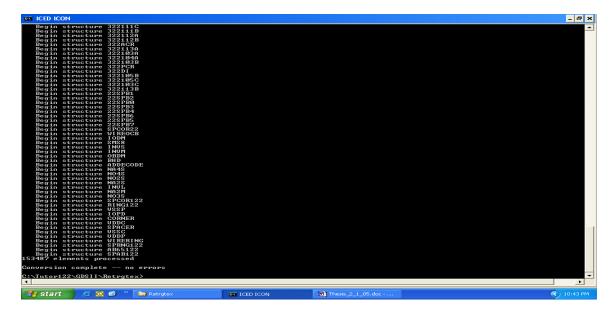

| FIGURE 3.25 DOS WINDOW AT THE COMPLETION OF PASS 2                          |     |

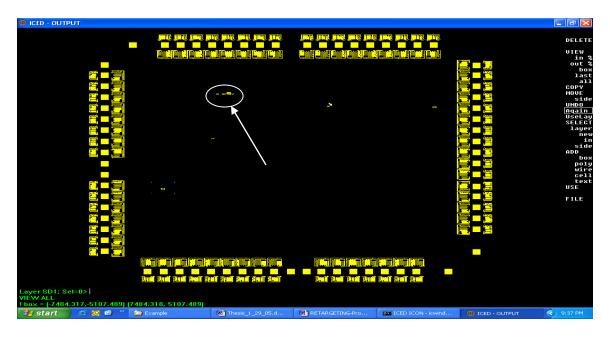

| FIGURE 3.26 COMPLETE LAYOUT OF THE W65C122S                                 |     |

| FIGURE 3.27 LAYOUT OF THE ADDRESS DECODER                                   | 89  |

| FIGURE 3.28 DOS WINDOW AFTER COMPILING THE RULES FILE                       | 90  |

| FIGURE 3.29 STARTING DRC IN THE CHIP VIEW                                   | 91  |

| FIGURE 3.30 DOS WINDOW AT COMPLETION OF DRC                                 | 92  |

| FIGURE 3.31 NEW OUTPUT CELL ICED WINDOW                                     | 93  |

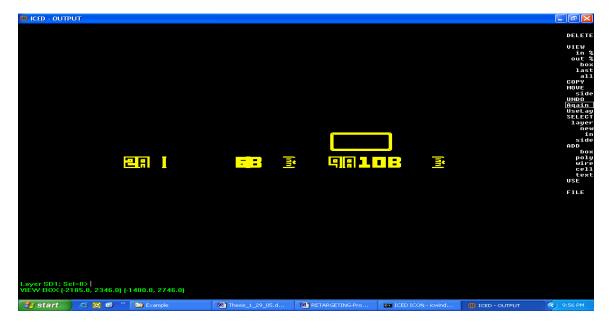

| FIGURE 3.32 OUTPUT CELL SHOWING DRC ERRORS                                  | 93  |

| FIGURE 3.33 CLOSE UP OF DRC ERRORS                                          | 94  |

| FIGURE 3.34 COMPLETION OF NLE RULES FILE COMPILATION                        | 95  |

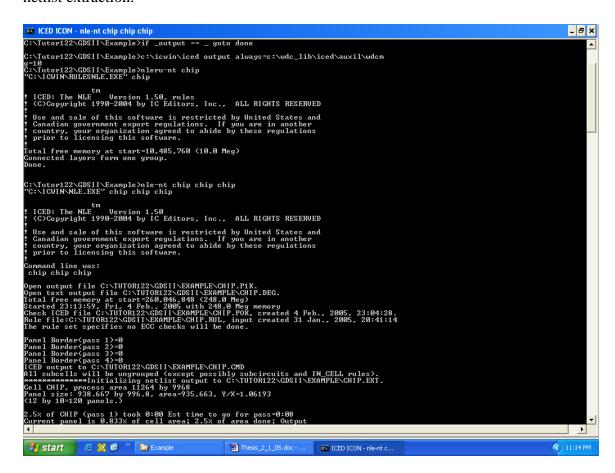

| FIGURE 3.35 INITIAL STAGE OF NETLIST EXTRACTION                             | 96  |

| FIGURE 3.36 MIDDLE STAGE OF NETLIST EXTRACTION                              | 97  |

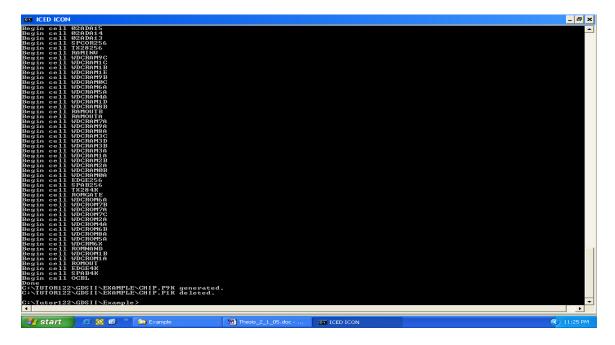

| FIGURE 3.37 COMPLETION OF NETLIST EXTRACTION                                | 97  |

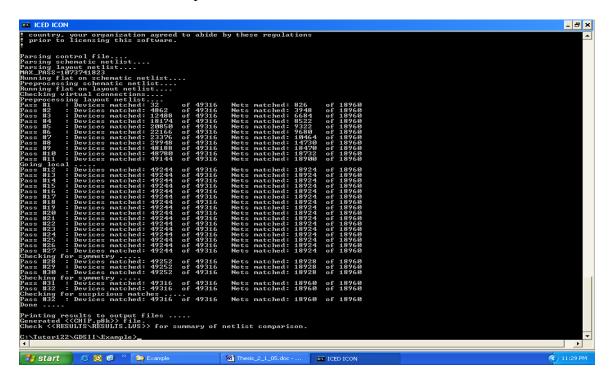

| FIGURE 3.38 RESULTS OF LVS                                                  | 99  |

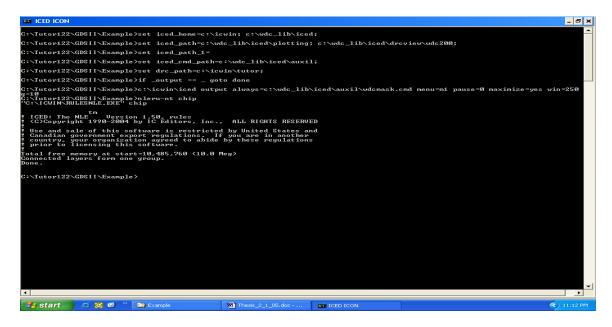

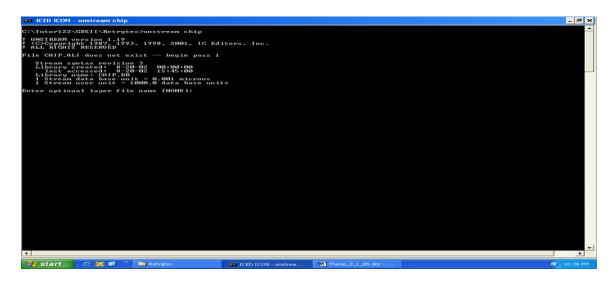

| FIGURE 3.39 FIRST PASS OF UNSTREAM PROCESS                                  | 102 |

| FIGURE 3.40 COMPLETION OF UNSTREAM PASS 1                                   | 102 |

| FIGURE 3.41 SECOND PASS OF UNSTREAM PROCESS                                 | 103 |

| FIGURE 3.42 COMPLETION OF UNSTREAM PASS 2                                   | 104 |

| FIGURE 3.43 CHIP VIEW WITH TSMC LAYERS                                      | 105 |

| FIGURE 3.44 PSPICE WAVEFORM WINDOW WITH DIGITAL AND ANALOG SIGNALS          | 108 |

# LIST OF TABLES

| TABLE 2-1 AMIS .5MICRON PROCESS DIFFUSION LAYER DESIGN RULES | 40 |

|--------------------------------------------------------------|----|

| TABLE 3.1 – FEATURES OF THE W65C122S                         | 60 |

| TABLE 3.2 SYSTEM MEMORY MAP                                  | 61 |

## 1. Introduction

#### 1.1 Background

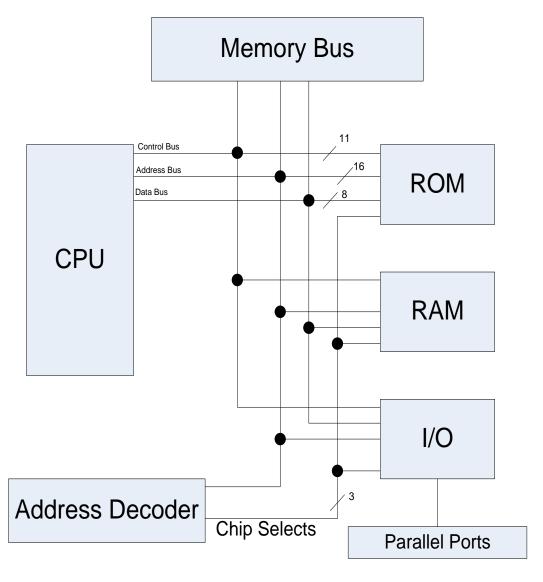

A major factor in the electronics industry today is to make devices that are small and fast, and to get these devices to market in the fastest time possible. With the many advances in process technology over the years, it is now possible to integrate whole systems on a single chip. In the past, a system consisted of a printed circuit board that had on it one chip for RAM (Random Access Memory), one chip for ROM (Read Only Memory), one chip for a microprocessor, one chip for I/O (Input/Output) capabilities, and perhaps chips for A to D (Analog to Digital) converters, D to A (Digital to Analog) converters, and UART's (Universal Asynchronous Receiver Transmitter). Today, one chip can contain a microprocessor core, RAM, ROM, I/O, A to D and so on. Thus we get the name System-on-a-Chip, (SOC). This is all possible due to VLSI (Very Large Scale Integration).

There are many aspects to VLSI design. There is the design of the system itself, which today is widely done using HDL's (Hardware Description Languages). The schematic entry method is also used in system design. This is widely done by dropping in reusable Intellectual Property (IP) cores into the design. These IP cores are proven to be reliable by the manufacturer and can help speed up the design process. Then there is the verification of the design, running simulations to determine if the design is working as expected. There is the layout of the design where the layers that make up the circuit are physically defined. Layout can be done by placing and routing the design manually, or it can be done by an automatic place and route tool. After the design has been laid out and verified, the final step is to target the design for a manufacturing process and send the

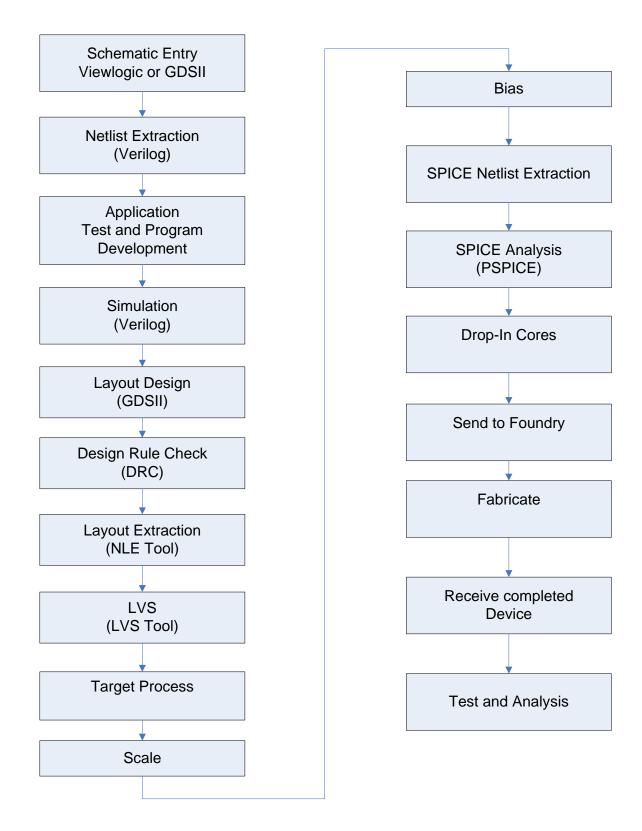

design out to be fabricated. Typically, prototypes are fabricated first, in small quantities, to keep expenses down in case the design is faulty. After evaluating the performance of prototype devices, the design needs to be reworked if there are problems, or sent for fabrication in larger quantities if the design is performing as expected. Figure 1.1 shows a flowchart for the system-on-chip design process that is used by The Western Design Center, Inc. (WDC). A class in VLSI design is instrumental in giving the student an introduction to the theory and tools that are used in the development of an SOC.

In the early days of system chip design, Negative Metal Oxide Semiconductor (NMOS) was the primary process used. The number of transistors on a single chip was in the thousands and the gate size was .5 microns or larger. The entire design process was very time-consuming as the circuit layout was manually compared to the circuit's schematics.

Over the years, the advent and refinement of HDL's has allowed designers to develop the chip by describing the design's hardware. Complementing HDL's, many tools were developed for design automation. These tools could place and route a design, perform a design rule check of the design, and simulate the design to ensure proper functionality.

Today, Complimentary Metal Oxide Semiconductor (CMOS) is the prevalent process used and transistor counts on a single chip are in the millions. The gate sizes of these transistors are .25 microns or less. Design automation has made the design of complex system chips faster and more efficient, cutting down on production time and increasing the time to market.

Figure 1.1 WDC flow chart for SOC design, manufacturing and test

#### 1.2 Problem

The original intent of this project was to develop a much needed laboratory manual that was to accompany the class UET 513 – Introduction to VLSI Design. This was a class that had been taught at ASU East for five years, without any structured lab to coincide with the theory presented. Unfortunately, UET 513 is no longer offered at ASU East, leaving a void for students interested in pursuing a career in VLSI design.

The focus of this project has shifted from an accompanying lab manual to a hands-on tutorial that will introduce students to the concept of reusable IP and to some of the tools that are used in creating a SOC. This tutorial will provide the student with the necessary means in understanding the VLSI design flow.

#### 1.3 Scope

The tutorial will introduce the students to the SOC design flow and the technology used at The Western Design Center Inc. WDC is located in Mesa, AZ, and was responsible for donating the computers, software tools, and IP that was used in UET 513. The intent of this tutorial is to provide an *introduction* to VLSI design. Each of the sections will introduce the student to a different software tool, or program, used in the SOC design flow. It is important to note that only the basic elements of the tools will be presented to the student. Again, the objective of the tutorial is to *introduce* the student to the tool, not make them experts in using the tool. The student will use technology already available to them, showing them the value of design reuse. This will give the student an appreciation of the tools available to them, and help them understand how VLSI design is done today.

#### 1.4 Assumptions

It is assumed that senior level undergraduate students and graduate students, will be using this tutorial, and will have had little or no prior experience in VLSI design, but have some knowledge of semiconductor terminology and theory. It is also assumed that a tutorial is necessary to assist the student in learning the tools and techniques used in the SOC design flow. Furthermore, it is assumed that the students will be using this tutorial at the offices of WDC, where the tools will be available for their use. If the student would like to perform this tutorial, the student must contact WDC, sign a Non-Disclosure Agreement (NDA), and arrange with WDC times that the student can go to the WDC office to use the design tools.

#### 1.5 Sequence of Presentation

Chapter 2 contains:

- Separate sections for each step of the design flow

- Introductory information about each step

- Introduction to the design tool used in each step

- Simple hands-on example demonstrating the usage of each tool

#### Chapter 3 contains:

- The tutorial using the components of the W65C122S SOC

#### Chapter 4 contains:

- Conclusions and recommendations

#### The Appendix contains:

- Information regarding Internships at The Western Design Center

- Contact information for The Western Design Center, Inc.

## 2. VLSI Design Flow

#### 2.1 Design entry

The first step in the VLSI design flow is creating, or entering, a design. "The purpose of design entry is to describe a microelectronic system to a set of electronic design automation (EDA) tools" (4:327)\*. There are two ways to accomplish this task. The first way is to enter the design via schematic entry, or schematic capture, where gates, symbols and interconnects are drawn using a computer program. The second way is to enter the design using a Hardware Description Language (HDL) such as Very High Speed Integrated Circuit Hardware Description Language (VHDL) or Verilog HDL. With this method, the designer describes the hardware by using software, and the code can be written using any text editor. After the code has been written, the code must be tested and debugged.

In the early 1980s, before the advent of schematic design entry tools, schematics were drawn using a graphics editor or drawn by hand. This provided a picture of the schematic with no functionality behind the schematic. From this picture, the designer manually coded the netlist of the circuit that was used for simulation. So in reality, HDLs were used before schematic entry tools for circuit design.

The Western Design Center, Inc. (WDC) has an interesting approach for their core designs in that they use the mask design editor to create a detailed "floor planning" schematic. The schematic can be edited and plotted on any Graphic Design System II (GDSII) editor, making it available to a wide range of users. GDSII is an Electronic Design Automation (EDA) industry standard binary format of the design that is used to transfer mask design data to a wafer fabrication shop (FAB).

<sup>\*</sup> Number in parenthesis indicates the reference at the end of this document.

The Verilog structural HDL is manually created by WDC and this corresponds to the GDSII schematic. This approach provides for complete control of naming every node manually, and helps in the mask design and debug phase of the design.

#### 2.1.1 Schematic entry

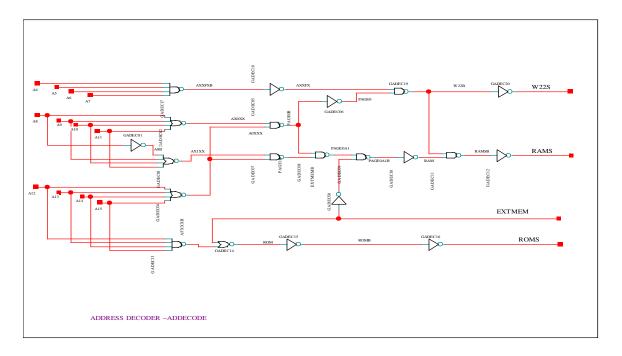

There are several powerful software programs that can be used to enter a design using schematic entry. Cadence Design Systems and Mentor Graphics make some of the more popular, widely used ones. With each of these programs, the designer can use the manufacturers' standard cell library, or import a custom cell library to draw the design. Figure 2.1 shows an example of a design that has been drawn using ViewDraw. ViewDraw is the schematic entry program in Mentor Graphics eProduct Designer (ePD) design suite. The schematic is the address decoder of the W65C122S.

Figure 2.1 Example of schematic entry – W65C122S address decoder

As can be seen in Figure 2.1, the schematic is a graphical representation of the design. This method is sometimes preferred because it provides an easily understood picture of the circuit. More importantly, it is not just a picture of the design, but a functional description of the design. The main goal in doing schematic design entry is to obtain an output file that can be used to simulate the circuit. Once the schematic is finished, the designer can extract a netlist of the design. This netlist is the output file that is used for circuit simulation. Circuit simulation will be discussed in section 2.2.

#### 2.1.2 Hardware Description Languages (HDLs)

There are two main HDLs used for design entry in industry today. One is VHDL and the other is Verilog HDL. While both packages are excellent at modeling hardware structures, there are differences in each one. Therefore, choosing the package to use depends on personal preferences, EDA tools available, business and marketing issues (4:10). Figure 2.2 shows a comparison of VHDL and Verilog HDL for a Serial Adder/Subtractor. For an in-depth comparison of the two languages, see (4:10-14).

#### 2.1.2.1 VHDL

VHDL "can be used to model a digital system at many levels of abstraction, ranging from the algorithmic level to the gate level" (1:1). With VHDL, the designer can describe the system in concurrent or sequential fashion, and may wish to include timing characteristics in the design.

There are four different ways to express the architecture of a system. The first is the structural method, where the system is "described as a set of interconnected components" (1:14). The second method is the data flow method, which uses concurrent

signal assignment statements. The third method is the behavioral method, where the system is described "as a set of statements that are executed sequentially in the specified order" (1:18). The last method is mixed style modeling which incorporates a mixture of the three previously mentioned methods.

#### 2.1.2.2 Verilog HDL

Described as an easy to learn and use HDL, Verilog HDL is a general-purpose HDL whose syntax is very similar to C and PASCAL. As with VHDL, systems can be described at different levels of abstraction. "The designer can define a hardware model in terms of switches, gates, RTL (register transfer level), or behavioral code" (3:7).

The highest level of abstraction is the behavioral level. At this level, the designer is concerned with describing the behavior of the circuit, and not how the circuit will be implemented using gates (3:115). At the data flow level, the system is described by specifying the actual data flow between registers, with knowledge on how this data is processed in the overall design. At the gate level, the system is described in terms of the individual logic gates and the interconnections between them. Finally, the switch level is the lowest level of abstraction, where the design "can be implemented in terms of switches, storage nodes, and interconnections between them" (3:16).

The designer is also able to mix each level of abstraction in the design. The combination of behavioral and data flow is commonly called RTL. When higher levels of abstraction are used, the design is more flexible and technology independent. Designs are more technology dependent and inflexible when lower levels of abstraction are used (3:16).

```

VHDL

Verilog

library IEEE:

module ADD_SEQ

use IEEE.STD_Logic_1164.all; IEEE.Numeric_STD.all;

(Clock, Reset, ParaLoad, CoeffData, Serialin,

EnableShiftAdd, ParallelOut);

entity ADD_SEQ is

Clock, Reset;

input

port (Clock, Reset: in std_logic;

ParaLoad, Serialin, EnableShiftAdd;

ParaLoad, Serialin, EnableShiftAdd: in std_logic;

input

(7:0) CoeffData;

output (7:0) ParallelOut;

CoeffData: in unsigned(7 downto 0);

ParallelOut: out unsigned(7 downto 0));

end entity ADD_SEQ;

ShiftRegA_LSB;

reg

reg

(7:0) ShiftRegA, ShiftRegB;

architecture RTL of ADD_SEQ is

Sum, Cout;

wire

component FULL_ADD

HoldCout;

reg

port (A, B, Cin: in std_logic; Sum, Cout: out std_logic;

end component:

always @(posedge Clock)

signal ShiftRegA, ShiftRegB: unsigned(7 downto 0);

begin: REG_AB

signal Sum, Cout, HoldCout: std_logic;

// Shift Register A

begin

REG_AB: process (Clock)

if (ParaLoad)

if rising_edge(Clock) then

ShiftRegA = CoeffData;

else if (EnableShiftAdd)

--- Shift register A

ShiftRegA_LSB = ShiftRegA(0);

if (ParaLoad = '1') then

ShiftRegA = ShiftRegA >> 1;

ShiftRegA <= CoeffData;

ShiftRegA(7) = ShiftRegA_LSB;

elseif (EnableShiftAdd = '1') then

Shift_RegA <= rotate_right(ShiftRegA, 1);</pre>

// Shift Register B

end if;

if (EnableShiftAdd)

--- Shift register B

begin

if (EnableShiftAdd = '1') then

ShiftRegB = ShiftRegB >>1;

ShiftRegB <= rotate_right(ShiftRegB ,1);</pre>

ShiftRegB(7) = Sum;

end if:

end if:

end process REG_AB;

assign ParallelOut = ShiftRegB;

ParallelOut <= ShiftRegB;

// Single bit full adder

--- Single bit full adder

FULL_ADD FA1

FA1: FULL_ADD port map

(.A(Serialin), .B(ShiftRegA(0)),

(A \Rightarrow ShiftRegA(0), B \Rightarrow ShiftRegB, 0),

.Cin(HoldCout),

(Cin => HoldCout, Sum => Sum, Cout => Cout);

.Sum(Sum), .Cout(Cout));

--- Hold carry out for next add

// Hold carry out for next add

HOLD_COUT: process (Clock, Reset)

begin

always @(posedge Clock or negedge Reset)

if (Reset = "0") then

begin: HOLD_COUT

HoldCout <= '0':

if (!Reset)

elseif rising_edge(Clock) then

HoldCout = 0;

if (EnableShiftAdd = '1') then

else if (EnableShiftAdd)

HoldCout <= Cout;

HoldCout = Cout;

else

else

HoldCout <= HoldCout;

HoldCout = HoldCout;

end if:

end

end process HOLD_COUT;

endmodule

end architecture RTL;

```

Figure 2.2 Comparison of VHDL and Verilog for a serial adder/subtractor

#### 2.1.3 Introduction to ViewDraw

As previously mentioned, The Western Design Center, Inc. uses ViewDraw for their schematic entry tool. ViewDraw is part of the Mentor Graphics ePD tool suite. This section will provide a basic introduction to ViewDraw, introducing the design environment, WDC's standard cell library, and the schematic editor.

#### 2.1.3.1 Introduction to creating a schematic in ViewDraw

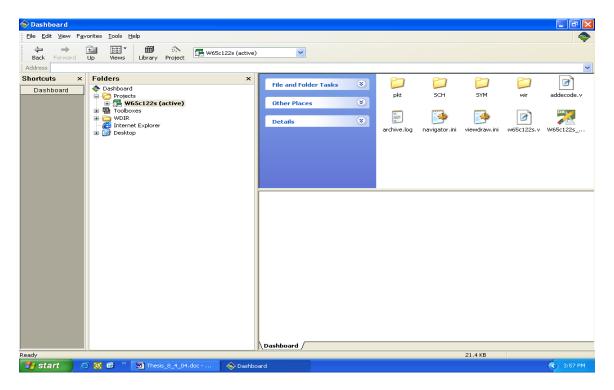

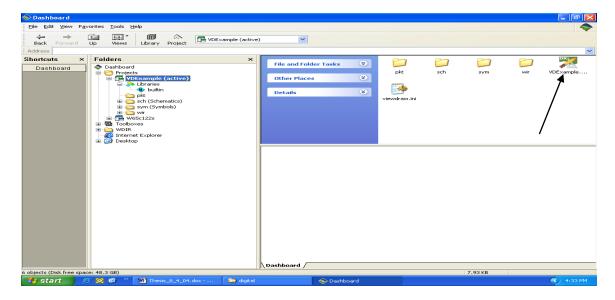

The first step in the process of drawing a schematic is to create a project where all libraries and design files are stored. To create a project, double-click on the eProduct Designer 2004 icon on the desktop. This will launch the ePD Dashboard, where the project is created and the project hierarchy is stored. After opening up Dashboard, your screen will look similar Figure 2.3.

Figure 2.3 ePD dashboard main window

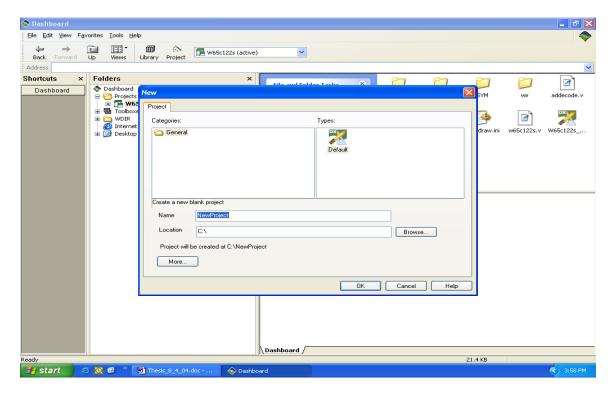

Click on File  $\rightarrow$  New  $\rightarrow$  Project. Your screen will look similar to Figure 2.4.

Figure 2.4 ePD new project window

In the Name field, type in a name for the project. For this example, type in VDExample for ViewDraw Example. Notice that the text below the Location field states that the project will be created in C:\VDExample. This can be changed by using the Browse button if desired, but for this example, we will not change this directory. Next, click OK. Your screen will look similar to Figure 2.5.

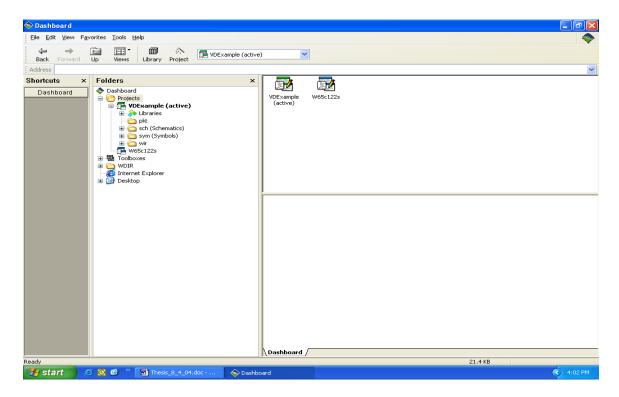

Figure 2.5 ePD dashboard view of projects

Figure 2.5 shows the Dashboard after the creation of the project VDExample. Notice that VDExample is listed in bold and has the word active next to it. This indicates that VDExample is the active project and any work done will be saved in the VDExample project hierarchy.

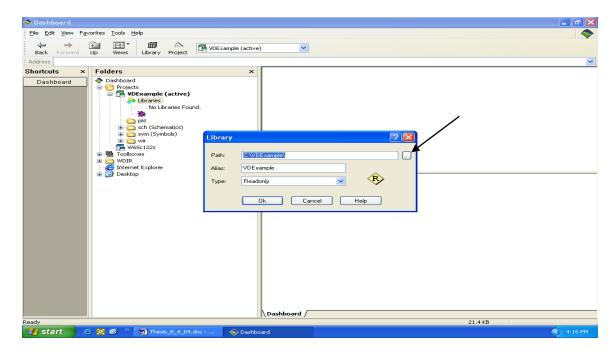

The next step is to import the library or libraries that we will use to create a schematic. The library will have all of the schematic symbols that will be placed onto the schematic drawing. For the purposes of this example, we will be using the builtin library that is standard with ViewDraw. To add this library, click on the Library icon on the toolbar. Your screen will look similar to Figure 2.6.

Figure 2.6 ePD add library window

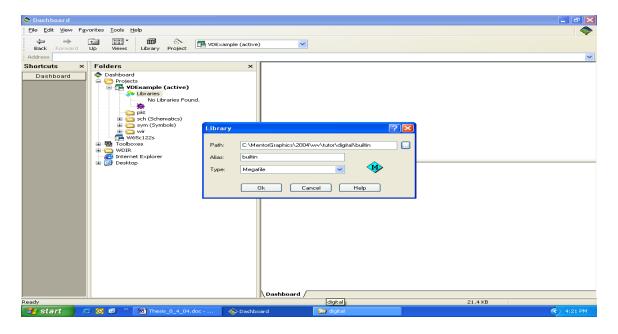

Click on the Browse button next to the Path field, as shown in Figure 2.6, and browse to the following directory: C:\MentorGraphics\2004\wv\tutor\digital. Select the builtin directory and click OK. Your screen will look similar to Figure 2.7.

Figure 2.7 ePD library window

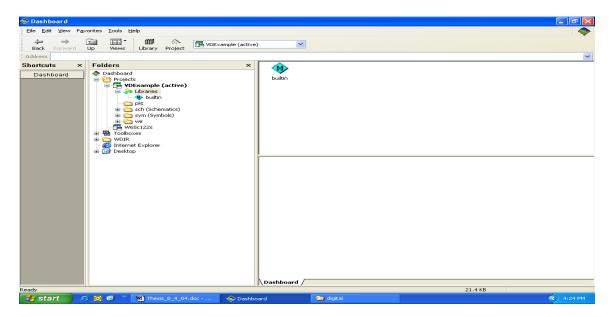

## Click OK. Your screen will now look similar to Figure 2.8.

Figure 2.8 ePD dashboard view with builtin library added

Notice now that the builtin library is listed under the Library directory, indicating that the library has been successfully added to the project. We are now ready to begin entering our schematic into ViewDraw. To do this, click on the project VDExample (active). Your screen will look similar to Figure 2.9.

Figure 2.9 ePD dashboard view of complete VDExample project

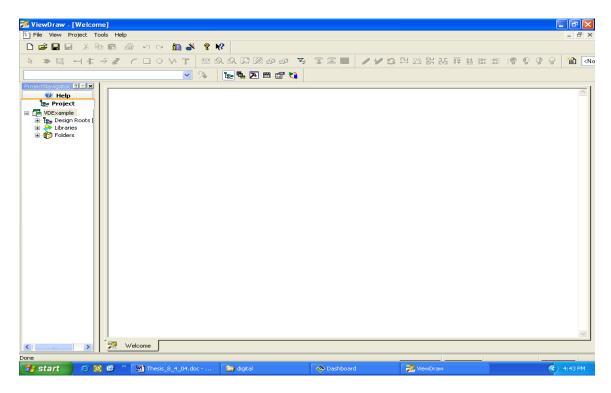

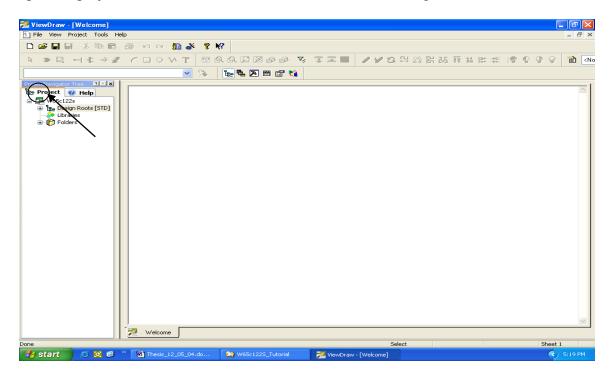

Double-click on the VDExample.dproj icon, as shown in Figure 2.9. This will automatically open up ViewDraw. **Note**: The software protection key, called a dongle, must be attached to the parallel port of the computer in order for ViewDraw to open. If ViewDraw is not opening, ask the system administrator at WDC to assist you. After ViewDraw opens, your screen will look similar to Figure 2.10.

Figure 2.10 ViewDraw main welcome window

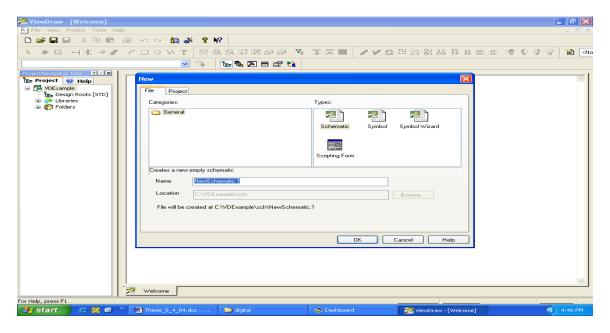

The first step is to create a new schematic drawing. To do this, click File  $\rightarrow$  New. Your screen will look similar to Figure 2.11.

Figure 2.11 ViewDraw new schematic window

This window has Schematic selected as the default. If for some reason Schematic is not selected, click on the Schematic icon to select it. In the Name field, type in a name for the schematic. For this example, type in VDExample and click OK. Your screen will look like Figure 2.12.

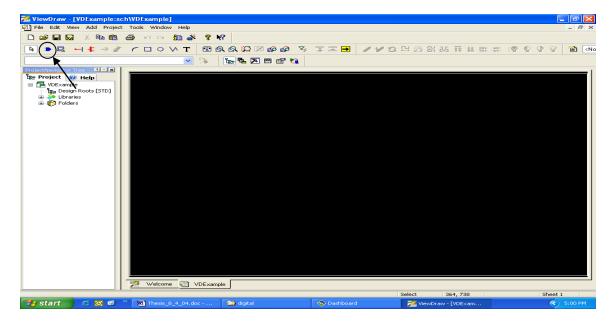

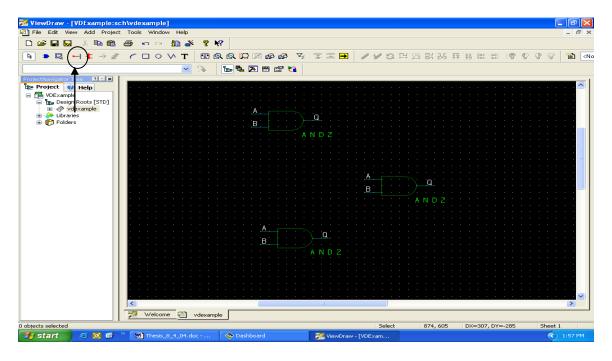

Figure 2.12 ViewDraw schematic window

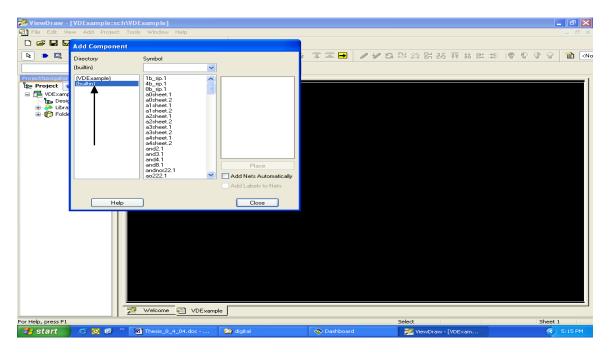

We are now ready to begin drawing a schematic. To draw a schematic, you have to pick components from the library, place them onto the schematic, and connect the pins by drawing wires from pin to pin. There are 2 ways to add a component. The first way is by clicking Add → Component from the Standard (File) toolbar. The second way is by clicking on the Component icon on the toolbar, shown in Figure 2.12. Using either method to add a component, your screen will look like Figure 2.13.

Figure 2.13 ViewDraw add component window

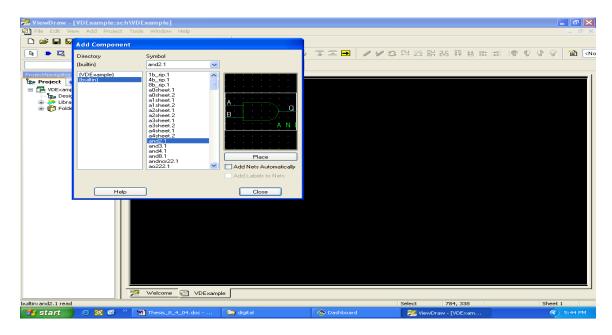

This window shows the available symbols in the builtin library. If the symbols are not listed, click on the builtin directory as shown in Figure 2.13. When a symbol is selected, a preview of the symbol is displayed in the preview window, as shown in Figure 2.14.

Figure 2.14 ViewDraw add component with preview window

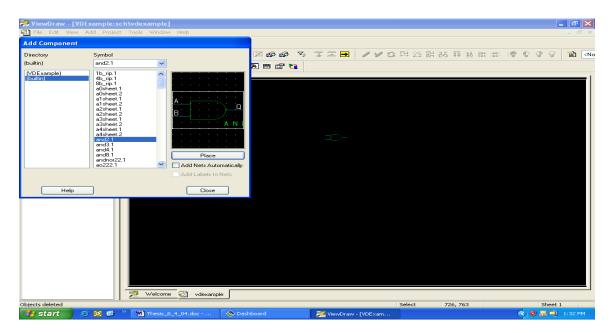

Here, a 2-input, AND gate is selected and the preview of the symbol is shown. To place the symbol onto the drawing, click the Place button and drag the mouse to the drawing window, as shown in Figure 2.15.

Figure 2.15 Symbol placement on schematic

Click the left mouse button to place the symbol onto the drawing area. Now, place a few more parts onto the drawing area. For this example, place two more 2-input, AND gates onto the drawing area. When complete, click the Close button on the Add Component window. Your screen will look similar to Figure 2.16.

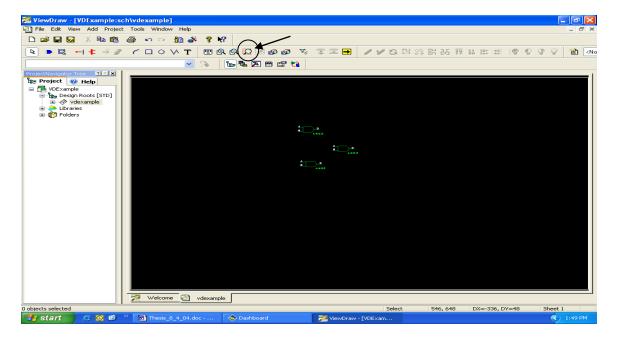

Figure 2.16 ViewDraw schematic window with added components

Next, zoom into the area of the three AND gates by clicking the Zoom Area icon on the toolbar as shown in Figure 2.16. Click this icon once to select it, then, using the mouse, draw a square around the three AND gates. To do this, place the cursor somewhere in the upper left corner of the top AND gate. Click and hold the left mouse button. Keeping the mouse button depressed, move the mouse down and to the right. You will see that a box is displayed as you move the mouse, showing the area that will be zoomed in on. Once you have the box around all three AND gates, release the mouse button. You will see that the AND gates have been magnified and that a grid now appears on the drawing. Your screen will look similar to Figure 2.17.

Figure 2.17 Schematic zoom view

Now, with the drawing grid in view, you can line up the symbols anyway that you want. To move the symbols around, place the cursor over the symbol you want to move, click and hold the left mouse button, and drag the symbol to the desired location. Release the mouse button when the symbol is at the desired location.

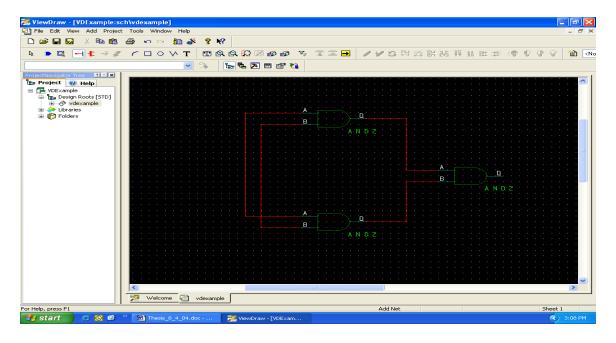

After the symbols are lined up, the next step is to connect the pins together using the wire command. Click on the Wire icon, as shown in Figure 2.17, to activate this mode. For this example, we will connect the A inputs of two AND gates to each other and the B inputs to each other. The outputs of each AND gate will connect to the inputs of the third AND gate. The purpose of this example is not to make a functional schematic, but to introduce you to the basic functions of ViewDraw.

In Wire mode, place the cursor at the A input of the topmost AND gate. Click and hold the left mouse button. Drag the cursor to the left for a few grid spaces. You will see that a wire is being drawn as you move the cursor. Releasing the mouse button will end

the wire at that location. Note that you are still in Wire mode. Now, place the cursor at the end of the wire you just drew. Click and hold the left mouse button and drag the cursor to the grid line that is associated with the A input of the bottom left AND gate. Release the mouse button to end the wire here. Again, place the cursor at the end of this wire, click and hold the left mouse button, and drag the cursor to the A input pin of the AND gate. Repeat this process to connect the B inputs together, as well as connecting the outputs of the left AND gates to the inputs of the right AND gate. When complete, your screen should look similar to Figure 2.18.

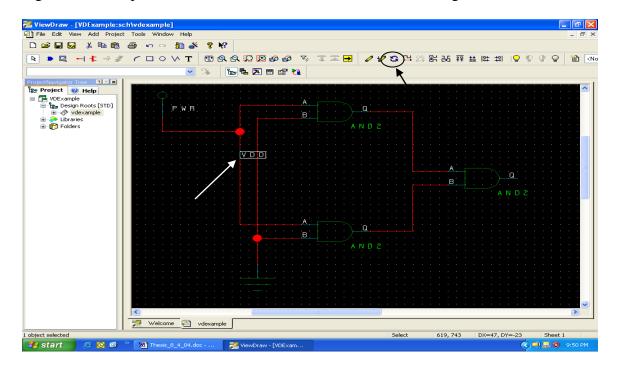

Figure 2.18 Example of schematic with components connected

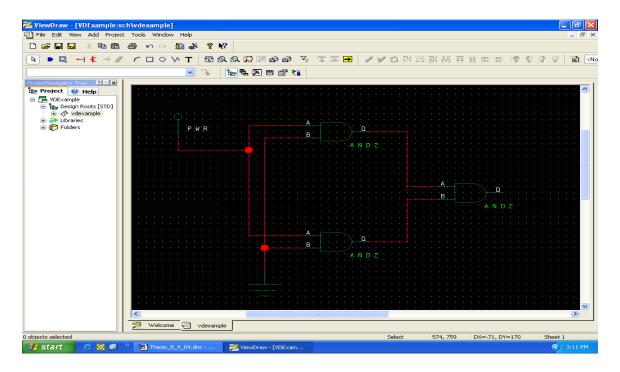

The next step is placing and connecting power and ground pins to the schematic. As discussed before, go to the Add Component window, select the **gnd** and **pwr** symbols and place them onto the schematic. Place the symbols and connect them up as shown in Figure 2.19.

Figure 2.19 Example of completed schematic

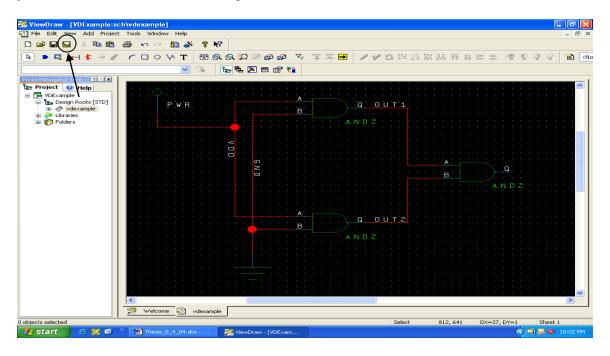

Next, we want to name the internal nets. For this example, we will name the power and ground nets as VDD and VSS respectively, and the outputs of the two AND gates OUT1 and OUT2. By default, ViewDraw automatically names any net connected to a **pwr** or **gnd** symbol VDD and VSS. However, for this exercise, we will rename these nets so that the name is visible on the schematic.

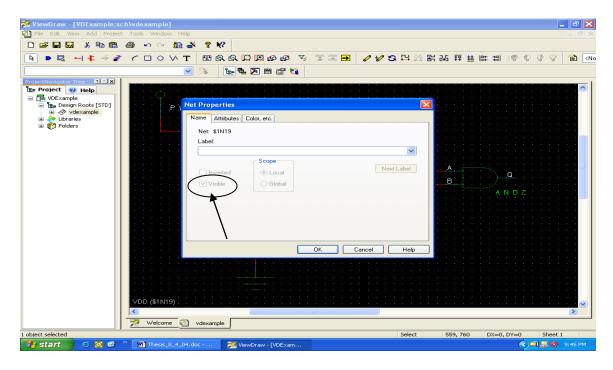

To name a net, place the cursor on any segment of the net and double-click the left mouse button. Do this for any segment of the net connected to the **pwr** symbol. A pop out window will appear and your screen will look like Figure 2.20.

Figure 2.20 Net properties window

In the Label field, type in VDD, verify that the Visible box is checked as shown in Figure 2.20, and press OK. Your screen will now look similar to Figure 2.21.

Figure 2.21 Schematic with net names visible

With the net name visible, you may want to move the location of the name. To do this, click on the name to highlight it as shown in Figure 2.21. Then, move the cursor over the name, press and hold the left mouse button, and drag the name to a good location. It may also be desirable to rotate the name. To rotate the name, select the name as described above and click on the Rotate icon, as shown in Figure 2.21. This will rotate the name 90 degrees each time this icon is clicked.

Follow the same procedure to name the three remaining nets. When completed, your screen will look similar to Figure 2.22.

Figure 2.22 Schematic with all net names visible

The final step in this example is saving and checking the schematic for errors. To save and check the schematic, click on the Save and Check icon on the toolbar, as shown in Figure 2.22. ViewDraw will save the schematic and check the design for any errors, such as unconnected pins or un-named nets. If any errors are found, an error message window will appear informing you of the errors and where they are on the schematic.

ViewDraw is a very powerful tool and has many more capabilities that are not in the scope of this example to discuss. It is recommended that the user gets more familiar with ViewDraw by using the online help features and getting started tutorials that are available within the tool itself.

#### 2.2 Design simulation

After the design has been entered using either of the above-mentioned methods, the design needs to be checked to verify its functionality. In the past, prototypes of the circuit were built and used to check the circuit. This method was feasible if designs were small and standard parts were used. With the complexity of today's circuits, prototyping is impractical. Therefore, for complex designs utilizing SOCs, ASICs, (Application-Specific Integrated Circuits) and FPGAs (Field Programmable Gate Arrays), a simulator is used to verify the designs functionality.

"Simulation is the fundamental and essential part of the design process for any electronic based product. Simulation is the process of verifying the functional characteristics of models at any level of behavior, from high levels of abstraction down to low levels" (4:14).

The simulator itself is a software tool that is used to simulate hardware models. Many times it is part of a design package, such as ePD, or can be a standalone tool such as Silos. With ePD, the designer can enter a design using schematic entry and perform a simulation of the design using one tool. Silos is strictly a Verilog HDL simulator, with no provisions for schematic entry.

Although The Western Design Center, Inc. uses ePD for schematic entry, they do not have a license for the simulation tool that is part of ePD. WDC uses Verilog as their

choice for design entry and they use Silos for all their simulations. This does not mean that schematics entered using ViewDraw cannot be simulated. ViewDraw has a utility called Verilnet, which is a Verilog netlister. When the Verilnet utility is run on a schematic, it creates a Verilog description of the schematic, called a netlist. The netlist describes all the components in the design and their interconnections. The netlist also includes the model parameters for the devices used in the design. This netlist is then used as the top level design that is used by the Silos Verilog simulator.

Along with the top level design or netlist, the simulator requires a stimulus file in order to perform a simulation. The stimulus file, or test bench, is a Verilog model that invokes the top level design and drives the different signals in the design. The test bench will usually have a clock defined in it and it will exercise each input with respect to the clock. For example, if the design is a two bit adder, the test bench will place a pattern of 1's and 0's on the adder's inputs. The output of the adder for the various input patterns can be stored in an output file, and this output file can be examined to verify that the adder is working properly.

The results can also be analyzed by viewing the waveforms that are generated by the simulator. By observing the waveforms, the designer can verify if operations are taking place when they are supposed to and if there are any conflicts. Using the adder example, if input A and input B are added together, the correct result should show up on the Sum output signal. If not, then there is a problem with the design and the design needs to be evaluated to find the problem. Once the functionality of the design has been verified, the designer can proceed to the next step in the design flow, the layout of the design. This is discussed in Section 2.3.

#### 2.2.1 Introduction to Silos

The Western Design Center, Inc. uses Verilog as their primary design entry format and WDC uses Silos as their Verilog simulator of choice. Silos is a product of Silvaco and can be used as a component in their suite of design tools, or used as a standalone tool. WDC uses Silos as a standalone tool. This section will give a brief introduction to Silos, describing the creation of a project, adding files to the project, performing a simulation and viewing the simulation results of a simple Verilog design.

## 2.2.1.1 Introduction to simulating a design using Silos

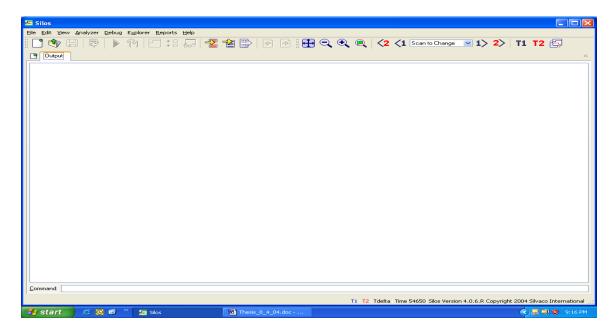

The first step to performing a simulation is to create a Silos project. All files used for the design and simulation are stored within this project. These files include the top level Verilog model of the design, the test bench files and any supporting library files. To begin, create a directory on the C:\ drive of the computer called C:\Silos\_Example. This will be where we will create the project and store the project files. Open up Silos by double-clicking on the Silos icon on the desktop. Note that Silos is protected by a hardware dongle, and this dongle must be attached to the computer's parallel port in order for Silos to open. After opening Silos, your screen will look like Figure 2.23.

Figure 2.23 Silos main window

Next, create a new project by clicking File → New Project from the menu toolbar.

This will cause the Create New Project window to appear and your screen will look like Figure 2.24.

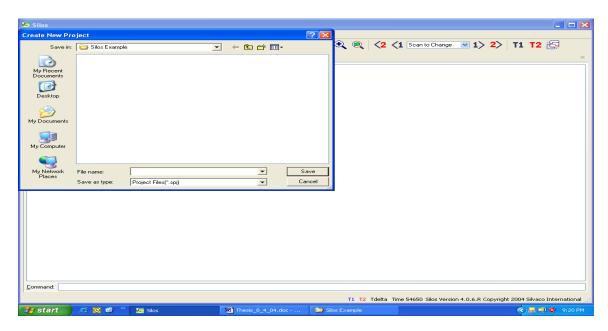

Figure 2.24 New project window in Silos

In the File name field, type in a name for the project. For this example, call the project Silos\_Example. The extension of the file name for a project is .spj. Browse to C:\Silos\_Example and click Save. After clicking Save, a Project Properties window appears and is shown in Figure 2.25.

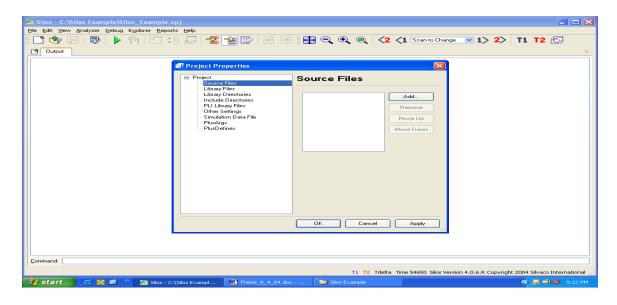

Figure 2.25 Silos project properties window

The Project Properties window will show all of the files that are associated with the project. At this time, we do not have any files to add to the project, so click Cancel to close this window. The screen will return back to the main Silos window.

Next, we must create the source and test bench files for our project. To demonstrate this, we will create the Verilog top level module and test bench of a 4-bit full adder. This example is taken from (7:206-208). The text for the files can be written in any text editor, such as WordPad or Notepad. Silos also has a text editor to enter source code. For this example, we will use the Silos text editor.

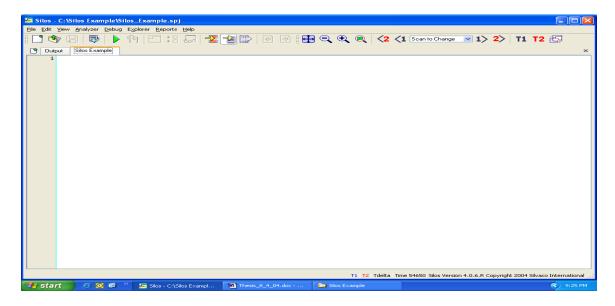

To create a new file in Silos, click File  $\rightarrow$  New. This will open a blank source window as shown in Figure 2.26.

Figure 2.26 Silos text editor window

Type the source code shown in Figure 2.27 into the text field. Notice that as you type, the editor changes the color of comments and Verilog reserved words, and adds line numbers.

```

module fourbitadder(sumout, carryout, ain, bin, cin, clock);

output [3:0] sumout;

output carryout;

input [3:0] ain, bin;

input cin, clock;

wire [3:0] ain, bin, sumout_tmp;

wire cin, carryout_tmp;

reg [3:0] sumout, ain_tmp, bin_tmp;

reg carryout, cin_tmp;

always @(posedge clock) begin

carryout = carryout_tmp;

sumout = sumout_tmp;

cin_tmp = cin;

ain_tmp = ain;

bin_tmp = bin;

end

assign {carryout_tmp,sumout_tmp} = ain_tmp + bin_tmp + cin_tmp;

endmodule

```

Figure 2.27 4-bit adder Verilog model (adder.v)

When you are done typing in the code, save the file to C:\Silos\_Example and name the file adder.v. Next, create a new file as described above and type in the test bench code shown in Figure 2.28.

```

module testbench;

wire [3:0] sumout;

wire carryout;

reg [3:0] ain, bin;

reg cin, clock;

integer i, j; parameter cycle = 100;

fourbitadder INST(sumout, carryout, ain, bin, cin, clock);

// adder4 INST(sumout, carryout, ain, bin, cin, clock

initial clock = 0; //non-synthesizable clock

always #(cycle/2) clock = ~clock; //generator

always @(posedge clock) begin

cin = 0; ain = 0; bin = 0;

for ( i=0; i \le 15; i = i + 1) begin

\#cycle ain = i;

for (j = 0; j \le 15; j = j + 1)

\#cycle bin = j;

end

\#cycle cin = 1;

for (i = 0; i \le 15; i = i + 1) begin

\#cycle ain = i;

for (j = 0; j \le 15; j = j + 1)

\#cycle bin = j;

end

#cycle $finish;

end

initial begin

$monitor("%0d", $time,, "clock = ", clock,

" cin = ", cin,

" ain[0] = ", ain[0],

" ain[1] = ", ain[1],

" ain[2] = ", ain[2],

" ain[3] = ", ain[3],

" bin[0] = ", bin[0],

" bin[1] = ", bin[1],

" bin[2] = ", bin[2],

" bin[3] = ", bin[3],

" s[0] = ", sumout[0],

" s[1] = ", sumout[1],

" s[2] = ", sumout[2],

" s[3] = ", sumout[3]);

end

endmodule

```

Figure 2.28 Test bench for the 4-bit full adder (test\_bench.v)

When you are done typing in the code, save the file to C:\Silos\_Example and name the file test\_bench.v. We are now ready to add the two files to the project that we created earlier.

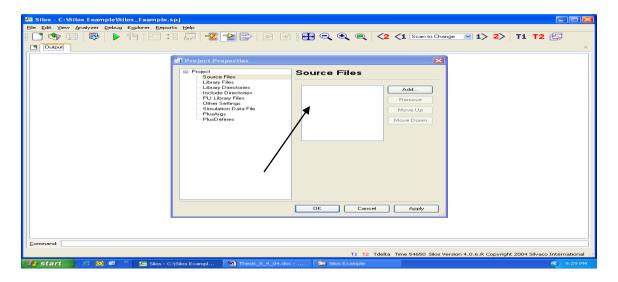

To add the files to the project, click on Edit → Project Properties. Your screen will look like Figure 2.29.

Figure 2.29 Silos project properties window

Next, click the Add button. This will bring up a file browser window, which defaults to the C:\Silos\_Example directory. The two files that we created adder.v and test\_bench.v are listed. There are two ways to add these files into the project; the quick method is to select each file while holding down the CRTL key, then click Add. This will add both files to the project at the same time. Alternately, you can select each file individually, then click Add, and repeat the process for the other file. After adding the files to the project, they are placed in the Source Files window, indicated in Figure 2.29. After adding both files to the project, your screen will look similar to Figure 2.30.

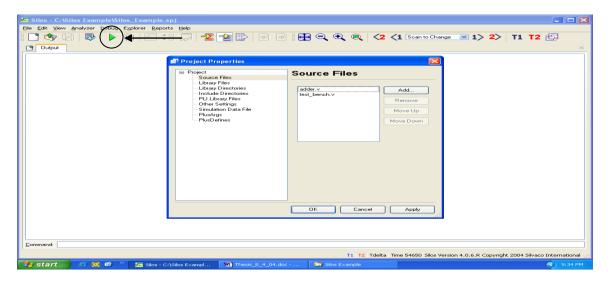

Figure 2.30 Silos project properties window with added files

Click OK to close the Project Properties window. The screen will return to the main Silos window.

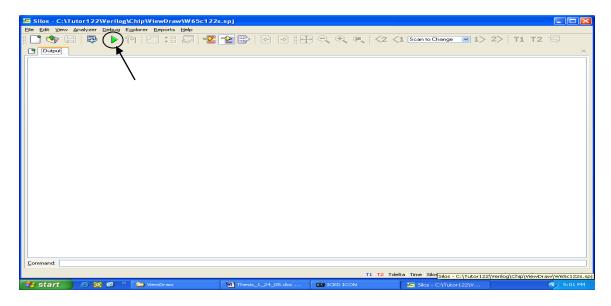

Now that the files have been added, the next step is to simulate the project. To do this, click the Start Simulation icon as indicated in Figure 2.30. If there are no errors in the source or test bench files, the simulation will begin and your screen will look similar to Figure 2.31.

Figure 2.31 Silos simulation result window

If an error was made in typing the source or test bench files, Silos will indicate the file name, error and the line number where the error is found. Debug the files as needed until the simulation runs correctly. The simulation will take a few seconds to complete.

Figure 2.31 shows the beginning stage of the simulation. Silos reads in the source and test bench files, checks them for errors, and then runs the simulation if no errors are found. The output shows the status of the clock, ain inputs, bin inputs and the sum outputs. This pattern continues until the \$finish line in the test bench file is executed.

Next, we want to look at some of the signals in a waveform view. To do this, we need to open the Explorer and Analyzer windows within Silos. To do this, click on the Analyzer and Explorer icons, as shown in Figure 2.31. After clicking each icon, your screen will look similar to Figure 2.32.

Figure 2.32 Silos analyzer and explorer window view

In the Explorer window, the module testbench is listed. Click the module name to select it. The signals that can be viewed are displayed. To add a signal to the Analyzer, select a signal to highlight it, then right-click over it to display a pop out menu. For example, select the signal clock to highlight it and then right-click the mouse. The screen should look like Figure 2.33.

Figure 2.33 Adding signals to the analyzer

In the pop out menu, click on the Add Signal(s) to Analyzer option. Your screen will now look similar to Figure 2.34.

Figure 2.34 Analyzer window with clock signal added

Repeat this procedure to add the ain, bin, cin and sumout signals to the Analyzer. Your screen should now look similar to Figure 2.35.

Figure 2.35 Analyzer window all signals added

Figure 2.35 shows only a small portion of the complete test. To view the signals in a different time scale, use the Zoom Out icon, shown in Figure 2.35. There is also a Zoom Full icon which will show all of the transitions for the whole time duration. However, this is not practical for analysis, as the signals are all compressed and not viewable. Click the Zoom Out icon a few times so that your screen looks similar to Figure 2.36.

Figure 2.36 Analyzer window with signals viewable

Note that the values of the registers are displayed within the waveform. This makes it easier to debug the project. Using the waveform view, the designer can monitor each signal with respect to the clock and analyze the output to see if the desired result is achieved. If the simulation results are correct, the design can move to the next step in the process. If the simulation produces incorrect results, the source files need to be debugged, corrected and re-simulated until proper functionality is achieved.

At this point, we have created a project, entered in the source code and test bench code, ran a simulation and viewed the simulation results. There are other features of Silos that are not in the scope of this introduction to discuss. It is recommended that the user get more familiar with Silos by utilizing the online help and tutorials available within Silos.

# 2.3 Physical layout of the design

The next step after design simulation is to do the physical layout of the design. The layout is done using an IC layout editor program. It is here that the design is laid out, as it will appear on silicon. The N and P regions of the transistors are defined, the polysilicon interconnect layers and the metal layers are drawn. In most cases, more than one layer is used. In this case, vias are used to provide interconnects between the layers. Figure 2.37 shows the physical layout of the Address Decoder used in the W65C122S.

Figure 2.37 Physical layout of the W65C122S address decoder

Once the layout has been completed, the layout must have a DRC (Design Rule Check) done on it. This is to insure that all design rules for the chosen technology have been followed. It checks for the correct spacing between poly lines, and the correct width of both poly and metal lines to name a few. Table 2-1 gives the American Microsystems Inc. Semiconductor (AMIS) standard diffusion layer design rules for their CMOS .5µ process.

Table 2-1 AMIS .5micron process diffusion layer design rules

| Rule   | Rule Description             | Rule | Units | Rule | Notes                                                                                                      |

|--------|------------------------------|------|-------|------|------------------------------------------------------------------------------------------------------------|

| Name   |                              |      |       | Type |                                                                                                            |

| DIFSP  | Min DIFfusion SPacing        | 0.90 | μm    | *    |                                                                                                            |

| DIFW   | Min DIFfusion Width          | 0.50 | μm    | *    | Resistors less than 0.8 µm wide do not meet Parametric Specs and are not modeled accurately in simulation. |

| TBEOND | TuB Enclosure Of N-Diffusion | 0.00 | μm    | *    | Well Tie Only                                                                                              |

| TBEOPD | TuB Enclosure Of P-Diffusion | 1.50 | μm    | *    |                                                                                                            |

| TBNDSP | TuB to N-Diffusion SPacing   | 1.50 | μm    | *    |                                                                                                            |

| TBPDSP | TuB to P-Diffusion SPacing   | 0.00 | μm    | *    | Substrate Tie Only                                                                                         |

| TRANW  | Minimum TRANsistor Width     | 0.80 | μm    | *    |                                                                                                            |

(Rule Type: \* Required, \*\* Recommended, Checked, \*\*\* Suggested, NOT Checked)

Once the layout has been completed and the DRC passes, the designer extracts a netlist of the layout, called NLE (NetList Extraction). The netlist describes the nodes and interconnects of the design. This netlist is used to perform an LVS (Layout versus Schematic) check. It is here that the schematic netlist is compared to the layout netlist. If the netlists match, the design can go to the final simulation before being sent out for fabrication. If the netlists do not match, the layout and the schematic need to be rechecked and corrected accordingly. In most cases, the mismatch lies within the layout, as the design has already been verified by simulation. For example, if in the schematic

point A is connected to point B, but in the layout point A is connected to point C, the LVS will detect the error and point the designer to the problem area.

WDC, as well as many other companies, have their own standard cell library and design rules that they use for their designs. These cells (NAND gates, NOR gates, I/O Pads, etc...) are laid out individually according to the design rules and then placed into a library. When a new circuit needs to be laid out, the parts are picked from the library and then placed into the layout drawing. "Placement is the task of placing modules adjacent to each other to minimize area or cycle time" (6:431).

After the cells or modules have been placed, the modules need to be connected together. There are two methods to connect up, commonly referred to as routing, the modules. The first method is to manually route the interconnections to each module, which can be time consuming, but can better optimize the design by minimizing the lengths of the interconnections. The second method is automatically routing the interconnections. The automatic routing tools need input files or algorithms in order to guide the routing process. There are tools that will also automatically place the cells or design blocks, as well as perform automatic routing. Automatic place and route tools are very powerful, high-end tools, therefore very expensive. WDC uses the manual place and route method to layout a design.

It is important to note that all of WDC's designs are done using WDC's proprietary, 2-micron retargetable design rules. Once the design is laid out using the WDC design rules, the DRC is done against these rules. If the DRC passes, NLE and LVS can be performed on the design. Once the design passes DRC and LVS, the design

can then be retargeted to a particular foundry for fabrication using the foundries design rules. This retargeting process will be discussed in Section 2.4.

#### 2.3.1 Introduction to ICED

There are many IC Layout tools available, some are very costly and very powerful tools and some are free to use for non-commercial purposes. WDC uses the IC EDitor (ICED) layout software. This software is widely used in the industry and it is also used to perform the DRC and LVS on the design.

Laying out a design is a very complex process and will take some time to learn how to do it properly. Teaching how to do layout is beyond the scope of this tutorial. However, this section will introduce the user to the ICED software, and discuss some of the basic operations that will be needed in Chapter 3. This section will not go into performing a DRC or LVS on a design.

#### 2.3.1.1 Working with ICED

As with the other software programs previously discussed, ICED is protected by a hardware key attached to the parallel port of the computer. Verify that this key is attached before working with ICED.

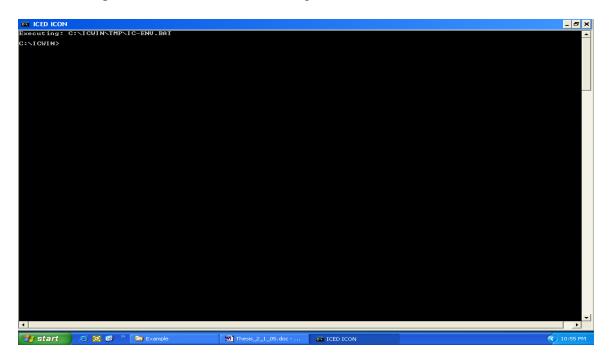

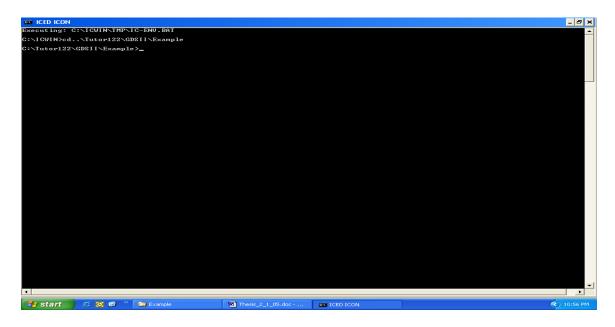

To begin, double-click on the ICED icon on the desktop of the ICED computer. You will get a DOS prompt as shown in Figure 2.38. ICED is designed to run using a DOS environment. We will utilize the C:\ICWIN\TUTOR directory for the remainder of this exercise. At the DOS prompt, change the working directory by typing: **cd tutor**. The DOS prompt should now read C:\ICWIN\TUTOR. Now, type: **del \*.\*** to erase the contents of the TUTOR directory.

Figure 2.38 ICED ICON DOS window

As previously mentioned, WDC has their own set of design rules that define the layers for the N-Well, Poly and Metal layers to name a few. These layer definitions are located in a command file that ICED calls when it is invoked.

To open ICED, you must call this command file and provide a cell name, for example, TEST. At the DOS prompt, type: **icwind test.** Your screen will look like Figure 2.39.

Figure 2.39 ICED editor window

ICWIND is the name of the command file that will start ICED and call all of the command files needed, including the file with the layer definitions.

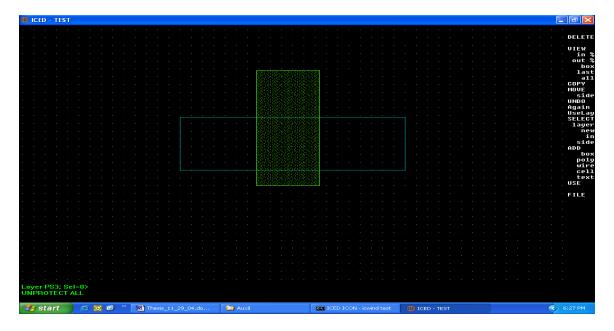

We are now ready to start drawing a cell. For this example, we will draw an NMOS transistor, introducing you to WDC's layers and some basic functions of ICED. First, click the UseLay option from the menu on the right side of the window. Your screen will look like Figure 2.40.

Figure 2.40 ICED editor window showing layer menu

The menu now shows the WDC layers. Click the layer called NW9, as this layer is the N-Well layer. Notice that the menu items have changed. To add a box for the N-Well, click Box from the menu. Draw a box in the drawing window, similar to the one shown in Figure 2.41. We are not concerned at this point with the size of the box, as we are not following any design rules. If we were drawing an actual gate to be used in a design, we would have to follow the design rules and draw the N-Well, and other layers, following these rules.

Figure 2.41 ICED editor window showing N-Well

Next, we want to draw a poly line. As before, click UseLay, then PS3 for the poly layer. Add a box to the drawing as shown in Figure 2.42.

Figure 2.42 ICED editor window showing N-Well and Poly layers

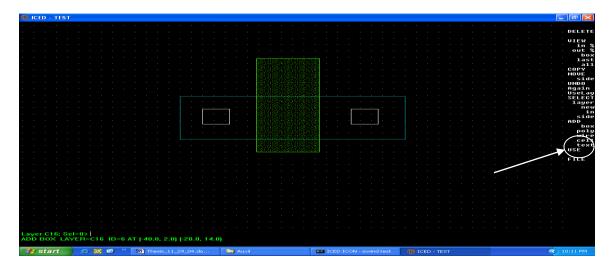

Next, we will add contacts to the source and drain regions. Again, click UseLay and select layer C16 for the contact layer. Add a box to the source and drain regions as shown in Figure 2.43.

Figure 2.43 ICED editor window showing NMOS transistor

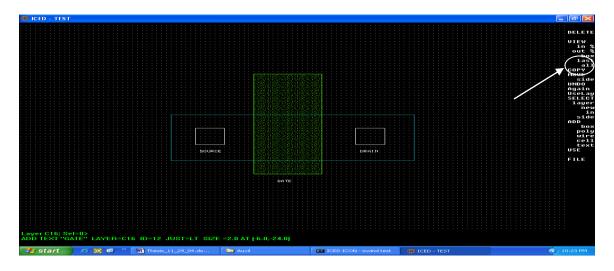

The last thing that we want to do is add some text to the drawing. To do this, Under the Add menu, click the Text option as shown in Figure 2.43. At the bottom of the screen will be a prompt reading Enter Text:. Type in Source and press Enter. This will add a box in a random location on the drawing. Using the mouse, move the text box to the source area and place the text box under the contact and press the left mouse button to anchor it. Do the same for the Drain and place the text for the Gate at the bottom of the poly line. When finished, your screen should look similar to Figure 2.44.

Figure 2.44 ICED editor window with text on drawing

Now, under the View menu, click All, as shown in Figure 2.44. This will reformat the drawing window and expand the drawing to maximize the view.

This concludes the introduction to ICED. At this point, if we were drawing this to follow a set of design rules, a DRC would have to be run to ensure that all rules were correctly followed. If a schematic of the transistor was created, we could also do an LVS to make sure that our schematic netlist matched the layout netlist.

This section discussed a few basic operations and briefly touched on the capabilities of ICED. Students are encouraged to follow the comprehensive tutorial provided by ICED in order to gain a better understanding of ICED and learn a few more of the basic functions. The tutorial is located in C:\ICWIN\DOC.

To exit out of ICED and save all of the work done, type Exit at the prompt in the lower left corner of the editor window and press Enter. This will save the design in the Tutor directory and the file will be called test.cel. The ICED ICON DOS window is still open at this point, and can be closed by typing Exit at the DOS prompt.

## 2.4 Scaling and sizing the design (Retargeting)

Once all of the above steps are complete, the design is ready to be prepared for fabrication. In order for fabrication to take place, a foundry and one of their processes have to be chosen as a target for the design. As an example, for the device to be fabricated using the AMIS  $.5\mu$  process, the transistors have to be scaled accordingly and the AMIS  $.5\mu$  design rules must be followed.

An existing design can also be retargeted for a different process within the same foundry. If a design was first manufactured using a foundries .25µ technology, it can now be manufactured using their .18µ technology by scaling the transistors.

Sizing means to adjust the widths and spacing of the lines after they have been scaled, with the result being that they pass the targeted processes DRC's. The Western Design Center, Inc. has a unique approach when it comes to sizing a design. WDC has developed an Excel spreadsheet that has their design rules entered in one column. Another column is where the design rules for the targeted process are entered. The spreadsheet is then run and any errors detected will be reported. If design rule violations exist, further scaling and/or selective biasing may be required. Sometimes rule violations are not critical and can be ignored. In this way, a design that is done using WDC's design rules can be retargeted to any manufacturing process.

"The main benefits of scaling are (1) smaller device sizes and thus reduced chip size, (2) lower gate delays, allowing higher frequency operation, and (3) reduction in power dissipation" (2:120). Due to the smaller device sizes, more devices can fit on a wafer, resulting in a higher yield per wafer. For more information on scaling MOS transistors, see (6:250-255).

Once the scaling, sizing and layer mapping to the targeted process have been completed, this information is then put into files that ICED will use to DRC the design for the targeted process. When the DRC passes, LVS must be run on the design to ensure there were no errors caused in the retargeting process. When the retargeted design passes the DRC and LVS, the design is now ready for PSPICE simulation to check the electrical and timing characteristics of the design.

### 2.5 Electrical characterization and timing analysis

In this part of the design flow, the circuit is checked for its electrical characteristics and more intensive timing analyses are performed. The electrical

characterization shows the operating voltages and currents throughout the design. The timing analysis will show switching times, set-up times, hold times and provide information on how fast the design will run. The timing analysis will also show the critical paths in the design. A critical path is the path that has the longest delay. If speed is a concern, the critical paths can be redesigned to minimize any delays.

Timing analysis can only be done after the layout, DRC, LVS and any retargeting steps have been completed. WDC uses PSPICE to perform timing analysis on designs. PSPICE, a Cadence Design Company product, is one of the more prevalent tools used to perform electrical characterizations on circuits.

In order for a PSPICE simulation to be performed, a netlist that can be read by PSPICE must be created. This PSPICE netlist is created from the netlist that was extracted from the layout using ICED. The netlist format created by ICED is not readable by PSPICE and needs to be converted into a PSPICE-readable netlist. WDC has created a PERL (Practical Extraction and Report Language) script that performs this conversion. Once the PSPICE netlist has been created, the PSPICE simulation can be performed.

# 2.5.1 Description of PSPICE simulation setup

This section will describe the files used for performing a PSPICE simulation and how to set up the PSPICE simulation. A PSPICE simulation takes about 10 hours to complete and is beyond the scope of this document to perform. The purpose of this section is to introduce WDC's concepts behind setting up a PSPICE simulation.

#### 2.5.1.1 The PSPICE simulation files

This section lists each of the files required to perform a PSPICE simulation and provides a description of each file.

- Filename.cir This CIRcuit file is the top level or project file for the simulation.

This file contains all of the files required for simulation.

- Digital.inc This file contains the Memory (RAM), A to D and D to A converters, buffers and logic circuitry that is used for the test setup.

- Model.inc This file contains the transistor and capacitor model parameters that are used for simulation. These model parameters are the target foundries model parameters. For example, if the device is to be manufactured on the TSMC .5μ process, this file would contain the TSMC .5μ transistor and capacitor models.

- Probe.inc This file contains the nodes that we want to look at and analyze after

the simulation has completed. Both analog and digital nodes are specified here.

- Stimulus.stm This is the file where the input signals needed for the simulation are defined. WDC uses a table to drive the inputs, referred to as table driven inputs.

- Netlist.net This file contains the actual netlist of the design that is used for the simulation. This is the file that was created by converting the layout netlist using the PERL script.

- Ram.ihx This file is used to program the RAM with the test data. The test data

in this file is in the Intel hex format.

#### 2.5.1.2 Setting up the PSPICE simulation

As previously mentioned, preparing for and running a simulation takes quite a long time and is beyond the scope of this tutorial. However, in order to gain an understanding of the process, the following section will describe the steps required for running a simulation using the W65C02S microprocessor as an example.

WDC has a folder on their file server called W65C02S, and in this folder are subfolders pertaining to various design steps for the W65C02S. The directory F:\W65C02S\PSpice\Example\Simulation contains the following files: W65C02.cir, digital.inc, model.inc, probe.inc, stimulus.stm, netlist.net and ram.ihx, as well as PSPICE generated files. These are the files that are required for simulation and these files have been described in Section 2.5.1.1. The transistor and capacitor model parameters that were used for the W65C02S simulation are the parameters of the Taiwan Semiconductor Manufacturing Corporation (TSMC) .5μ process. If a different TSMC process is to be used, the model parameters in model.inc will have to be changed while all other files remain the same. Copy the F:\W65C02S\PSpice\Example\Simulation directory to your C:\ drive so as not to alter the source directory.

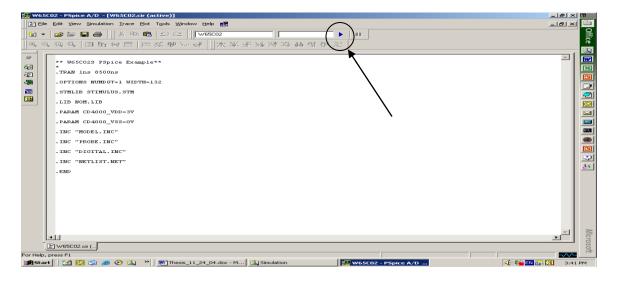

To begin, the file W65C02.cir is opened by double-clicking it. This automatically opens PSPICE and Figure 2.45 shows the opening window.

Figure 2.45 PSPICE main window

Figure 2.45 shows the contents of the .CIR file and lists the time that the simulation is to run to, parameter declarations, and file names for running the simulation.

As previously mentioned, the simulation will take about 10 hours to complete, therefore it will not be performed here. However, the following will describe the process for completeness. A simulation is started by clicking on the blue arrow as shown in Figure 2.45. There will be some activity in the bottom right hand corner of the PSPICE window. It will give the percentage completed of the simulation and the time in  $\mu$ s where the simulation is currently running at.

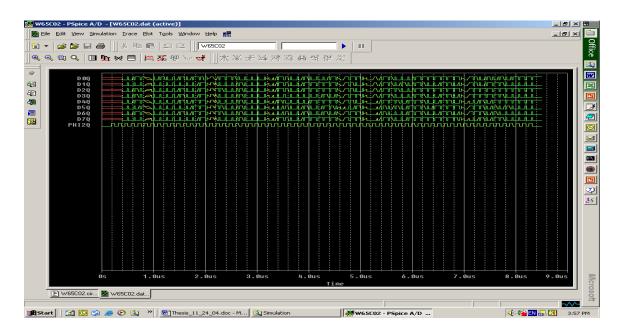

When the simulation is completed, PSPICE creates a data file, a vector file and other files that are associated with the simulation. To view the waveforms, open the data file W65C02.dat by double-clicking it. Figure 2.46 shows the data (waveform) window.

Figure 2.46 PSPICE waveform window

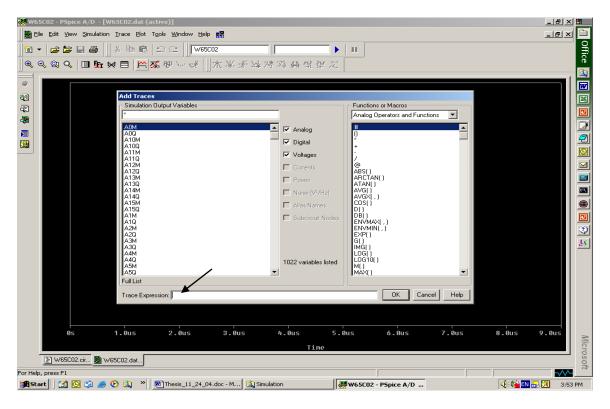

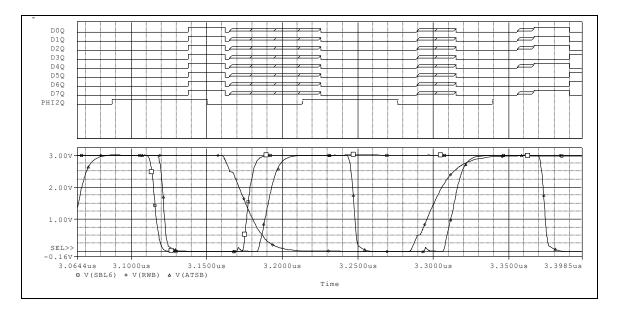

To add the signals that you want to analyze, click the Add Trace icon as shown in Figure 2.46. This will cause a pop-out window to appear and your screen will look like Figure 2.47.

Figure 2.47 PSPICE add trace window